Конференции

Self-Timed Fused Multiply-Add Unit Performance Improvement

Igor A. Sokolov, Yury A. Stepchenkov, Yury V. Rogdestvenski, Yury G. Diachenko, Asta V. Rogdestvenskene, Denis Y. Diachenko. Self-Timed Fused Multiply-Add Unit Performance Improvement // 2022 IEEE Conference of Russian Young Researchers in Electrical and Electronic Engineering (EIConRus) St. Petersburg, Moscow, Russia, January 25-28, 2022. — IEEE, 5 P.

Indexed in WoS, Scopus.

Повышение сбоеустойчивости самосинхронного троичного умножителя

Дьяченко Ю.Г., Степченков Ю.А., Рождественский Ю.В., Морозов Н.В., Степченков Д.Ю., Рождественскене А.В. Повышение сбоеустойчивости самосинхронного троичного умножителя // Проблемы разработки перспективных микро- и наноэлектронных систем (МЭС). 2021. Выпуск 2. С. 70-76.

DOI:10.31114/2078-7707-2021-2-70-76. (Индексируется в РИНЦ).

URL: http://www.mes-conference.ru/data/year2021/pdf/D015.pdf.

Library reference: Diachenko Yu.G., Stepchenkov Yu.A., Rozhdestvenskij Yu.V., Morozov N.V., Stepchenkov D.Yu., Rogdestvenskene A.V. Improvement of Ternary Self-Timed Multiplier Soft Error Tolerance // Problems of Perspective Micro- and Nanoelectronic Systems Development — 2021. Issue 2. P. 70-76.

Финансовая поддержка: Исследование выполнено при финансовой поддержке Министерства науки и высшего образования Российской федерации (проект No 075-15-2020-799) в Институте проблем информатики ФИЦ ИУ РАН. / Funding Agency: The research was supported by the Ministry of Science and Higher Education of the Russian Federation (project No. 075-15-2020-799).

Аннотация: Самосинхронные (СС) схемы в большей степени устойчивы к кратковременным логическим сбоям, чем их синхронные аналоги, благодаря СС-кодированию информационных сигналов, двухфазной дисциплине функционирования и запрос-ответному взаимодействию частей СС-схемы. Специальные схемотехнические и топологические приемы позволяют дополнительно повысить их естественную сбоеустойчивость. В значительной мере это обеспечивается использованием нового принципа индикации СС-сигналов. Классическая индикация строится на основе детектирования единственного спейсерного состояния информационного СС-сигнала в предположении, что остальные состояния являются разрешенными рабочими состояниями. Но при наличии логического сбоя это предположение оказывается неверным. Статья описывает способ повышения помехоустойчивости одноразрядного троичного СС-сумматора и умножителя на его основе. Приведены вероятностные оценки устойчивости исходного и улучшенного в этом отношении умножителя к кратковременным логическим сбоям. Показано, что за счет усложнения индикации одноразрядного сумматора и соответствующего увеличения на 27% аппаратных затрат умножителя 54×54 достигается увеличение времени его бессбойной работы в 1,9 раза.

Abstract: Self-timed (ST) circuits are more short-term soft error tolerant than their synchronous counterparts due to the ST coding of information signals, two-phase operation discipline, and request-acknowledge interaction of ST circuit’s parts. Special circuitry and layout techniques make it possible to increase their natural failure tolerance further. New ST signal indication principles essentially ensure this. The classical ST indication detects a single spacer state of the information ST signal. It assumes that the remaining states are only allowed working states. However, in the presence of a soft error, this assumption turns out to be incorrect. The article describes a method for increasing the noise immunity of a one-bit ternary ST adder and a multiplier based on this adder. It presents probabilistic soft error tolerance estimates for the original and improved multiplier in this respect. It is shown that due to the complication of a one-bit adder’s indication and the corresponding 27% increase in the hardware costs of the multiplier 54×54, its failure-free operation time rises by 1.9 times.

Сравнение сбоеустойчивых синхронных и самосинхронных схем

А.А. Зацаринный, Ю.А. Степченков, Ю.Г. Дьяченко, Ю.В. Рождественский. Сравнение сбоеустойчивых синхронных и самосинхронных схем // Математическое моделирование в материаловедении электронных компонентов. ММMЭК–2021. 25–27 октября 2021 г., Москва: Материалы III Международной конференции (сборник тезисов). – Москва: МАКС Пресс, 2021. С. 154-156.

DOI: 10.29003/m2498.ММMSEC-2021/154-156.

URL: https://mmhs.frccsc.ru/conferences/mmmsec2021/files/mmmsec2021.pdf.

Library reference: A.A. Zatsarinny, Yu.A. Stepchenkov, Yu.G. Diachenko, Yu.V. Rogdestvenski. Failure tolerant synchronous and self-timed circuits comparison // Mathematical Modeling in Materials Science of Electronic Components. MMMEC-2021. October 25–27, 2021, Moscow : Proceedings of the international conference (Collection of bstracts). – Moscow : MAKS Press, 2021. P. 154-156.

Финансовая поддержка: Исследование выполнено в рамках государственного задания № 0063-2019-0010. / Funding Agency: The study was carried out within the framework of state assignment No. 0063-2019-0010.

Аннотация: Статья рассматривает проблему разработки синхронных и самосинхронных (СС) цифровых схем, устойчивых к логическим сбоям. В синхронных схемах для обеспечения устойчивости к однократному сбою традиционно используется принцип голосования «2-из-3», приводящий к увеличению аппаратных затрат в три раза. В СС-схемах, благодаря парафазному кодированию сигналов и двухфазной дисциплине функционирования, даже дублирование обеспечивает уровень защиты от логического сбоя в 2,1–3,5 раз выше, чем троированный синхронный аналог. Разработка новых средств высокоточного моделирования механизмов возникновения сбоев в микроэлектронных компонентах позволит получить более точные оценки сбоеустойчивости электронных схем.

Abstract: The article considers the problem of developing synchronous and self-timed (ST) digital circuits that are tolerant to soft errors. Synchronous circuits traditionally use the 2-of-3 voting principle to ensure single failure, resulting in three times the hardware costs. In ST circuits, due to dual-rail signal coding and two-phase control, even duplicatio n provides a soft error tolerance level 2.1 to 3.5 times higher than the triple modular redundant synchronous counter part. The development of new high-precision software simulating microelectronic failure mechanisms will provide more accurate estimates for the electronic circuits’ failure tolerance.

Реализация синтеза самосинхронных схем в базисе БМК

Плеханов Л. П., Денисов А. Н., Дьяченко Ю.Г., Мамонов Д.И., Морозов Н.В., Степченков Д.Ю. Реализация синтеза самосинхронных схем в базисе БМК // Российский форум «Микроэлектроника – 2021». 7-я Научная конференция «Электронная компонентная база и микроэлектронные модули» Сборник тезисов. Алушта (Республика Крым), 03.10-09.10.2021, Наноиндустрия, – М: Техносфера, 2021. Спецвыпуск Т.14, № 7S, 2021 – с. 395-397.

DOI: 10.22184/1993-8578.2021.14.7s. (Индексируется в РИНЦ).

URL: https://disk.yandex.ru/d/FonzjCZ61JLVMA/.

Library reference: Plekhanov L. P., Denisov A. N., Diachenko Yu. G., Mamonov D. I., Morozov N. V., Stepchenkov D. Y. Implementing Self-timed Circuit Synthesis in Gate Array Basis // Russian Forum «Microelectronics — 2021». 7th Scientific Conference «Electronic Component Base and Microelectronic Modules». Collection of abstracts. Alushta (Republic of Crimea), 03.10-09.10.2021, Nanoindustry Russia – Technosphera JSC, Moscow 2021. Special Issue 14, № 7S, 2021 – P. 395-397.

Финансовая поддержка: Исследование выполнено в рамках государственного задания № 0063-2019-0010. / Funding Agency: The study was carried out within the framework of state assignment No. 0063-2019-0010.

Аннотация: Доклад посвящен реализации автоматизированного синтеза самосинхронных (CC) схем на основе описания схемы на языке Verilog и библиотеки стандартных элементов 5503СС, расширенной специфичными для СС-схем элементами. Программа синтеза имеет графический интерфейс и интегрируется в САПР полузаказных БИС «Ковчег» (МИЭТ).

Abstact: The report describes automated self-timed (ST) circuit synthesis implementation on a base of the circuit’s Verilog-description and the standard cell library 5503CC, extended with the cells specific to ST circuits. The synthesis program has a graphic user interface. It is integrated into gate array CAD «Kovcheg» (MIET).

Self-Timed Storage Register Soft Error Tolerance Improvement

Yury Stepchenkov, Yury Diachenko, Yury Rogdestvenski, Yury Shikunov, Denis Diachenko. Self-Timed Storage Register Soft Error Tolerance Improvement // Proceedings of IEEE East-West Design & Test Symposium (EWDTS’2021), Batumi, Georgia, September, 10 — 13, 2021, P. 145-150.

DOI: 0.1109/EWDTS52692.2021.9580993. (Indexed in Scopus).

URL: https://ieeexplore.ieee.org/document/9580993.

Финансовая поддержка: Исследование выполнено при поддержке Российского научного фонда (проект 19-11-00334). / Funding Agency: The research was supported by the Russian Science Foundation (project No. 19-11-0034).

Abstract: The paper examines the self-timed (ST) pipeline register’s tolerance to soft errors in the pipeline stage’s combinational part and in itself. It aims to analyze the known storage register bit’s circuit cases and improve its soft error tolerance. The use of failure tolerant ST coding, which treats the anti-spacer state as a spacer, increases the ST pipeline’s failure tolerance level. Layout techniques of spacing the dual-rail signal component sources at a distance of more than 2 µm from each other reduce the number of failure types in the ST circuits. In particular, switching the dual-rail signal from a correct working state to an inverse one becomes unrealizable. Circuitry techniques, including cross-connections and local feedback, prevent the bit of the ST-pipeline register from sticking in the anti-spacer state and significantly increase the register’s insensitivity to single soft errors. The use of a DICE-like C-element with two in-phase outputs instead of a known circuitry solution ensures the immunity of the register bit for soft errors inside it. All proposed techniques improve the ST circuit’s soft error tolerance level from 76% to 95%.

Аннотация: Статья исследует устойчивость регистра самосинхронного (СС) конвейера к логическим сбоям в комбинационной части ступени конвейера и в нем самом. Использование сбоеустойчивого СС-кодирования, рассматривающего антиспейсерное состояние как спейсер, повышает уровень сбоеустойчивости СС-конвейера. Топологические методы разнесения формирователей компонент парафазного сигнала на расстояние более 2 мкм друг от друга сокращают число типов сбоев в СС-схемах. В частности, переключение парафазного сигнала из корректного рабочего состояния в инверсное рабочее состояние становится нереализуемым. Схемотехнические методы, включающие перекрестные связи и локальную обратную связь предотвращают «залипание» разряда регистра СС-конвейера в состоянии антиспейсера и существенно повышают устойчивость регистра к однократным кратковременным логическим сбоям. Использование DICE-подобного С-элемента обеспечивает иммунность разряда регистра к логическим сбоям внутри его ячеек памяти.

Дополнительную информацию о содержании доклада вы можете получить на сайте конференции / You can get additional information on the content of the article on the conference website. Также вы можете связаться с авторами доклада, или с руководителем научной группы Степченковым Ю. А. ia_ste@mail.ru / You can also contact the authors of the report, or with the head of the scientific group Stepchenkov Ya. A. ia_ste@mail.ru.

Improvement of Self-Timed Pipeline Immunity of Soft Errors

Yury A. Stepchenkov, Yury V. Rogdestvenski, Yury I. Shikunov, Denis Y. Diachenko, Yury G. Diachenko. Improvement of Self-Timed Pipeline Immunity of Soft Errors // 2021 IEEE Conference of Russian Young Researchers in Electrical and Electronic Engineering (EIConRus) St. Petersburg, Moscow, Russia, January 26-29, 2021. — IEEE, P. 2045-2049.

DOI: 10.1109/ElConRus51938.2021.9396125. Indexed in Scopus.

URL: https://ieeexplore.ieee.org/abstract/document/9396125.

Финансовая поддержка: Исследование выполнено при финансовой поддержке Министерства науки и высшего образования Российской федерации (проект No 075-15-2020-799) в Институте проблем информатики ФИЦ ИУ РАН. / Funding Agency: The research was supported by the Ministry of Science and Higher Education of the Russian Federation (project No. 075-15-2020-799).

Abstract: The paper presents the results of a study of self-timed (ST) digital circuits’ soft-error tolerance. Practical ST circuits have a pipeline structure. The combinational parts of the ST pipeline are naturally immune to 72% of short-term soft errors. The proposed circuitry and layout methods increase the ST pipeline combinational part’s failure tolerance to 98% and higher. ST pipeline stage register is the most susceptible to soft errors. A typical variant of the ST pipeline register bit unit based on C-elements has a failure tolerance of 83%. The proposed register bit implementation cases increase the failure tolerance of the ST pipeline up to 98%.

Аннотация: Статья представляет результаты исследования сбоеустойчивости самосинхронных (СС) цифровых схем. Практические СС-схемы имеют конвейерную структуру. Комбинационная часть СС-конвейера естественно иммунна к 72% кратковременных логических сбоев. Предложенные схемотехнические и топологические методы увеличивают сбоеустойчивость комбинационных частей СС-конвейера до уровня 98% и выше. Регистр ступени СС-конвейера наиболее восприимчив к логическим сбоям. Типовой вариант разряда регистра СС-конвейера, реализованный на С-элементах, имеет уровень сбоеустойчивости 83%. Предлагаемые реализации разряда регистра увеличивают сбоеустойчивость СС-конвейера до 98%.

Дополнительную информацию о содержании доклада вы можете получить на сайте конференции / You can get additional information on the content of the article on the conference website. Также вы можете связаться с авторами доклада, или с руководителем научной группы Степченковым Ю. А. ia_ste@mail.ru / You can also contact the authors of the report, or with the head of the scientific group Stepchenkov Ya. A. ia_ste@mail.ru.

Самосинхронные схемы как база создания высоконадежных

высокопроизводительных компьютеров следующего поколения

А. А. Зацаринный, Ю. А. Степченков, Ю. Г. Дьяченко, Ю. В. Рождественский. Самосинхронные схемы как база создания высоконадежных высокопроизводительных компьютеров следующего поколения // Математическое моделирование в материаловедении электронных компонентов. ММMЭК–2020. 19–20 октября 2020 г., Москва: Материалы II Международной конференции. – Москва : МАКС Пресс, 2020. – С 114-116. ISBN 978-5-317-06483-9

DOI: https://doi.org/10.29003/m1506.ММMSEC-2020

Аннотация: В работе предлагаются конструктивные и схемотехнические решения для реализации высокопроизводительных компьютеров следующего поколения. Они основаны на методологии проектирования самосинхронных схем и обеспечивают повышение устойчивости вычислительных систем к логическим сбоям, являющимся следствием наведенных помех и радиационного воздействия.

Повышение сбоеустойчивости индикации самосинхронных схем

Ю. А. Степченков, Ю. Г. Дьяченко, Ю. В. Рождественский, Н. В. Морозов, Д. Ю. Степченков, Д. Ю. Дьяченко. Повышение сбоеустойчивости индикации самосинхронных схем // Проблемы разработки перспективных микро- и наноэлектронных систем — 2020. Сборник трудов / под общ. ред. академика РАН А.Л. Стемпковского. М.: ИППМ РАН, 2020. Выпуск 2. С. 66-72. DOI: 10.31114/2078-7707-2020-2-66-72

Аннотация: Сложность и площадь топологической реализации индикаторной подсхемы самосинхронной (СС) схемы составляют до 50% от сложности и площади всей СС-схемы. Соответственно, вероятности появления кратковременного логического сбоя, вызываемого ионизационным током из-за внешних причин, в индикаторной подсхеме и в остальной части СС-схемы примерно одинаковы. Сбоеустойчивость индикаторной подсхемы определяется ее иммунностью к логическому сбою в индицируемой СС-схеме и сбоеустойчивостью основного компонента индикации – гистерезисного триггера (Г-триггера). Использование DICE реализации Г-триггера существенно повышает сбоеустойчивость индикаторной подсхемы. В статье предлагается заменить двухтранзисторный конвертор в DICE-реализации Г-триггера четырехтранзисторным конвертором и использовать Г-триггеры с синфазными входами и выходом для организации «дерева» индикаторных элементов, формирующих общий индикаторный выход СС-схемы из частичных индикаторных сигналов. В совокупности с элементами «равнозначность» или «неравнозначность» в качестве первого каскада индикаторной подсхемы такой подход обеспечивает абсолютную защиту от логического сбоя в индикаторной подсхеме и анти-спейсера в индицируемой схеме.

Abstract: Adverse external influences (nuclear particles, cosmic rays, electromagnetic impulses) and internal disturbances (interference from adjacent signal traces, noises on power buses, and substrate) give rise to long-term (memory bit upset) and short-term (soft error) effects that affect digital circuit performance. Clock frequency rising increases the likelihood of writing soft error to synchronous register and makes synchronous circuits more sensitive to soft errors. An alternative to synchronous circuits are the self-timed ones. They are more immune to the soft errors due to dual-rail data coding and switching completion indication ensuring handshaking between their parts. The self-timed circuit’s indication sub-circuit occupies 25% through 50% of the entire self-timed circuit’s hardware and layout area. So, short-term soft errors, caused by ionization events and interference inductions, appear in the indication subcircuit with a probability comparable to the soft error appearance probability in the self-timed circuit rest part. Indication subcircuit soft error tolerance depends on its immunity to soft errors in the indicated self-timed circuit and failure protection of Muller’s C-element that is an indication base component. XOR and XNOR cells at the indication subcircuit first stage mask so-called anti-spacer state that is one-third part of the soft errors appeared in indicated circuits. Dual interlocked C-element implementation increases the indication subcircuit failure tolerance, but not sufficiently. The article proposes to replace the two-transistor converter in the dual interlocked C-element with a four-transistor converter and to use C-elements with in-phase inputs and output for building an indication “tree” combining all partial indication signals into a total one. Together with the XOR cell at the indication subcircuit first stage, the proposed approach provides an absolute protection against both soft errors in indication subcircuit and anti-spacer in the indicated self-timed circuit.

Метод повышения быстродействия самосинхронного умножителя

Ю. В. Рождественский, Ю. А. Степченков, Ю. Г. Дьяченко, Н. В. Морозов, Д. Ю. Степченков, Д. Ю. Дьяченко. Метод повышения быстродействия самосинхронного умножителя // Проблемы разработки перспективных микро- и наноэлектронных систем — 2020. Сборник трудов / под общ. ред. академика РАН А.Л. Стемпковского. М.: ИППМ РАН, 2020. Выпуск 1. С. 82-88. DOI: 10.31114/2078-7707-2020-1-82-88

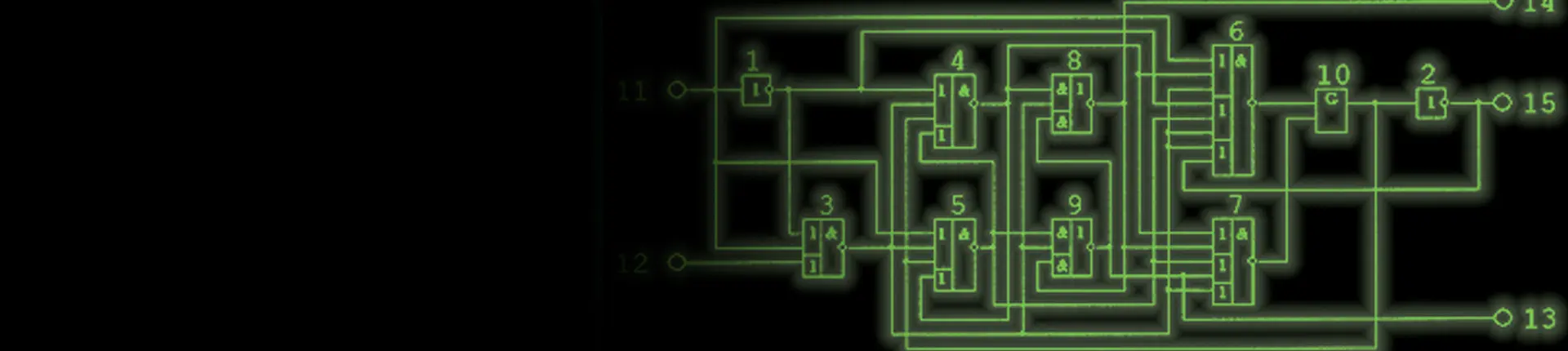

Аннотация: Быстродействие самосинхронных (СС) схем в значительной степени определяется их индикаторной подсхемой. Особенно остро эта проблема стоит в многоразрядных вычислительных СС-схемах, в том числе, в умножителе. Классическая индикация предполагает формирование общего индикаторного выхода для всей СС-схемы, участвующего в запрос-ответном взаимодействии СС-устройств или ступеней СС-конвейера. Многоразрядные СС-схемы, реализующие алгоритмы обработки данных с высокой степенью параллелизма, допускают использование групповой индикации выходов СС-схемы с формированием поразрядных сигналов управления фазами их входов. Статья описывает метод ускорения работы индикаторной подсхемы применительно к СС-умножителю, реализующему модифицированный алгоритм Бута и использующему двухступенчатое «дерево» Уоллеса на сумматорах с избыточным (троичным) и парафазным СС-кодированием их входов и выходов. Поразрядное управление входами обеих ступеней конвейера «дерева» Уоллеса обеспечили повышение быстродействия СС-умножителя 54*54 на 40% за счет увеличения его аппаратных затрат на 2,3-2,5%.

Abstract: Self-timed (ST) circuit’s indication subcircuit largely determines its performance. This problem is especially acute in multi-bit computing ST circuits, including multiplier. The classical indication involves generating an entire ST circuit total indication output, which takes part in handshaking ST units or ST pipeline stages. Multi-bit ST circuits that implement data processing algorithms with a high parallelism degree allow the use of group indication of the ST circuit outputs resulting in bitwise signals controlling their inputs’ phase. The article describes a method of accelerating the indication subcircuit operation as applied to the ST-multiplier, which implements the modified Booth algorithm and uses the two-stage Wallace tree on adders with redundant (ternary) and dual-rail ST-coding of their inputs and outputs. Group indication and bitwise input control of both Wallace tree pipeline stages provide an increase in ST-multiplier performance by 40% with a penalty of 2.3-2.5% in its hardware.

Increasing Self-Timed Circuit Soft Error Tolerance

Igor Sokolov, Yury Stepchenkov, Yury Diachenko, Yury Rogdestvenski, Denis Diachenko. Increasing Self-Timed Circuit Soft Error Tolerance // 2020 IEEE EAST-WEST DESIGN & TEST SYMPOSIUM Varna, Bulgaria, September 4 – 7, 2020, P. 450-454 . (is indexed in Scopus).

DOI: 10.1109/EWDTS50664.2020.9224705

Abstract: Indication subcircuit is an essential part of the selftimed circuits. It provides acknowledgment of the self-timed circuit switching completion and ensures correct handshake interaction between functional blocks. Besides, indication subcircuit complexity is comparable with the indicated self-timed circuit’s complexity. So short-term soft errors, induced by the external and internal causes in both the indication subcircuit and the indicated self-timed circuit, are equally dangerous. Indication subcircuit soft error tolerance depends, the first, on its immunity to soft errors in the indicated self-timed circuit and, the second, on its failure protection. The first aspect becomes lower critical due to the XOR cell on the first stage of the indication subcircuit. An appropriate circuitry basis decreases indication subcircuit sensitivity to the possible soft errors induced in it. Static and semistatic Muller’s C-element is a traditional base component used for indication purposes. Its dual interlocked implementation improves the indication subcircuit failure protection against soft errors in its internal nodes, but not sufficiently. The article proposes a new C-element’s schematic that fully tolerates it against the soft errors in all internal nodes. Besides, using Celements with in-phase inputs and output in an indication pyramid ensures indication subcircuit protection against soft errors induced at the output of the C-elements. The proposed approach makes an indication subcircuit fully protected against all soft errors induced in it.

Дополнительную информацию о содержании доклада вы можете получить на сайте конференции или связавшись с авторами доклада / You can get additional information on the content of the article on the conference website or by contacting the authors of the article.

Self-Timed Circuitry Retrospective

Victor Zakharov, Yury Stepchenkov, Yury Diachenko, Yury Rogdestvenski. Self-Timed Circuitry Retrospective // 2020 International Conference Engineering Technologies and Computer Science EnT 2020 Moscow, Russia24-27 June 2020. P. 58-64. (indexed in Scopus).

DOI: 10.1109/EnT48576.2020.00018

Abstract: The paper compares synchronous and self-timed methodologies for designing digital circuits. Self-timed circuits proposed by D. Muller in the mid-twentieth century have several advantages over synchronous counterparts. They maintain functional performance at any cell delays, do not require global synchronization, and identify constant failures. The data redundancy and associated hardware redundancy provide these self-timed circuit properties. The practical design of self-timed units of varying complexity has proven the effectiveness of self-timed solutions, especially in highly reliable and fault-tolerant applications. The paper presents the resultsof comparative measurements of test chips of synchronous and self-timed circuits, the performance, and immunity evaluations of self-timed circuits of different complexity levels. The proposed method of group indication of multi-bit self-timed circuits increases their performance by 40% due to a slight increase (less than 3%) in hardware complexity.

Аннотация: Статья посвящена сравнению синхронной и самосинхронной методологий проектирования цифровых микросхем. Самосинхронные схемы, предложенные Маллером Д. в середине двадцатого века, обладают рядом преимуществ по сравнения с синхронными аналогами. Они сохраняют функциональную работоспособность при любых задержках элементов, не требуют глобальной синхронизации, выявляют константные неисправности. Эти свойства самосинхронных схем обеспечиваются избыточным кодированием данных и связанной с ним аппаратной избыточностью. Практическая разработка самосинхронных устройств разной сложности доказала эффективность самосинхронных решений, особенно в высоконадежных и отказоустойчивых применениях. Статья приводит результаты сравнительных испытаний тестовых кристаллов синхронных и самосинхронных схем, оценки быстродействия и иммунности самосинхронных схем разного уровня сложности. Предложенный метод групповой индикации многоразрядных самосинхронных схем повышает их быстродействие на 40% за счет незначительного увеличения (менее 3%) аппаратных затрат.

Дополнительную информацию о содержании доклада вы можете получить на сайте конференции / You can get additional information on the content of the article on the conference website. Также вы можете связаться с авторами доклада, или с руководителем научной группы Степченковым Ю. А. ia_ste@mail.ru / You can also contact the authors of the report, or with the head of the scientific group Stepchenkov Ya. A. ia_ste@mail.ru.

Improvement of the Quasi Delay-Insensitive Pipeline Noise Immunity

Yuri Stepchenkov, Anton Kamenskih, Yuri Diachenko,Yuri Rogdestvenski, and Denis Y. Diachenko. Improvement of the Quasi Delay-Insensitive Pipeline Noise Immunity // The 11th International Conference on Dependable Systems, Services and Technologies (DESSERT’2020) Ukraine, Kyiv, May 14-18, 2020, P. 47-51. (indexed in Scopus).

DOI: 10.1109/DESSERT50317.2020.9125021

Abstract: the paper examines the immunity of Quasi Delay-Insensitive (QDI) circuits to soft errors caused by noises. The considered noise sources are internal and external events: layout wires crosstalk, interference on the power and ground buses, electromagnetic pulse. The paper suggests using the failsafe QDI circuits discipline and layout methods that reduce dual-rail signal sensitivity to noises. Indication of dual-rail signal forbidden state as a spacer increases QDI circuits immunity to soft errors. Using a modified C-element to implement a pipeline stage register bit reduces the danger of the pipeline deadlock. It improves the immunity of the QDI pipeline to the noise soft errors by 11% (up to 97.8%).

Аннотация: Статья исследует устойчивость квази-нечувствительных к задержкам (Quasi Delay-Insensitive, QDI) схем к логическим сбоям, вызванным шумами. Источником рассматриваемых шумов являются внутренние и внешние события: перекрестные наводки трасс в топологии, наводки по шинам питания и земли, электромагнитный импульс. Статья предлагает использовать сбоеустойчивую дисциплину QDI схем и топологические методы, снижающие чувствительность парафазных сигналов к шумам. Индикация запрещенного состояния парафазного сигнала как спейсера обеспечивает повышение устойчивости QDI схем к логическим сбоям. Использование модифицированного С-элемента для реализации разряда регистра ступени конвейера снижает опасность критического останова конвейера и улучшает устойчивость QDI конвейера к шумовым логическим сбоям на 11% (до 97.8%).

Дополнительную информацию о содержании доклада вы можете получить на сайте конференции / You can get additional information on the content of the article on the conference website. Также вы можете связаться с авторами доклада, или с руководителем научной группы Степченковым Ю. А. ia_ste@mail.ru / You can also contact the authors of the report, or with the head of the scientific group Stepchenkov Ya. A. ia_ste@mail.ru.

Self-Timed Multiply-add-subtract Unit Alternates

Yury A. Stepchenkov, Yury G. Diachenko, Yury V. Rogdestvenski, Denis Y. Diachenko, Yury I. Shikunov. Self-Timed Multiply-add-subtract Unit Alternates // 2020 IEEE Conference of Russian Young Researchers in Electrical and Electronic Engineering (EIConRus) Moscow, Russia, January 27-30, 2020. — IEEE, P. 1864-1868. (indexed in Scopus).

DOI: 10.1109/EIConRus49466.2020.9039039

Abstract: Paper presents the results of a study of the selftimed fused multiply-add-subtract unit (FMAS) alternates. All FMAS alternates comply with the IEEE 754 standard and use the modified Booth algorithm to multiply two input 64-bit operands, followed by the addition and subtraction of the third operand. They differ from each other by internal signals self-timed coding: dual-rail, redundant ternary, or redundant quaternary code. The paper analyzes and compares their features, offers their optimized pipeline implementations and recommendations for their use. FMAS alternates have approximately the same performance but different hardware costs and layout sizes.

Аннотация: Представлены результаты исследования вариантов самосинхронного устройства умножения с последующим сложением и вычитанием (УСВ). Все варианты УСВ соответствуют стандарту IEEE 754 и используют модифицированный алгоритм Бута для умножения двух входных 64-разрядных операндов с последующим сложением-вычитанием третьего операнда. Они отличаются друг от друга кодированием внутренних сигналов: парафазным, избыточным троичным или избыточным четверичным кодом. Статья анализирует и сравнивает их свойства, предлагает их оптимизированные конвейерные реализации и рекомендации по их применению. УСВ варианты имеют примерно одинаковую производительность, но различные аппаратурные затраты и размеры топологии.

Дополнительную информацию о содержании доклада вы можете получить на сайте конференции / You can get additional information on the content of the article on the conference website. Также вы можете связаться с авторами доклада, или с руководителем научной группы Степченковым Ю. А. ia_ste@mail.ru / You can also contact the authors of the report, or with the head of the scientific group Stepchenkov Ya. A. ia_ste@mail.ru.

Fault-Tolerance of the Self-Timed Circuits

Yuri A. Stepchenkov, Anton N. Kamenskih, Yuri G. Diachenko, Yuri V. Rogdestvenski, and Denis Y. Diachenko. Fault-Tolerance of the Self-Timed Circuits // 2019 10th International Conference on Dependable Systems, Services and Technologies (DESSERT). (indexed in Scopus).

DOI: 10.1109/DESSERT.2019.8770047.

Abstract: the paper discusses a fault-tolerance problem for digital integrated circuits. Due to their properties, self-timed circuits, unlike synchronous counterparts, are immune towards the greater part of the short-term logical faults. Indication of an illegal state of the dual-rail signal as second spacer increases fault-tolerance of the combinational selftimed circuits up to 82%. Self-timed triggers, due to their indication features, are immune to 44% logical faults. The use of special methods of doubling transistors and bistable cells, which are the basis of the self-timed triggers, enhances their fault-tolerance up to 80%.

Аннотация: Статья посвящена проблеме надежности цифровых интегральных микросхем. Благодаря своим свойствам, самосинхронные схемы, в отличие от синхронных аналогов, иммунны по отношению к большей части кратковременных логических сбоев. Реализация индикации запрещенного состояния парафазного сигнала как второго спейсера повышает сбоеустойчивость комбинационных самосинхронных схем до 82%. Самосинхронные триггеры, благодаря своей индикации, невосприимчивы к 44% логических сбоев. Использование специальных методов дублирования транзисторов и RS-триггеров, составляющих основу самосинхронных триггеров, обеспечивает повышение их сбоеустойчивости до уровня 80%.

Дополнительную информацию о содержании доклада вы можете получить на сайте конференции / You can get additional information on the content of the article on the conference website. Также вы можете связаться с авторами доклада, или с руководителем научной группы Степченковым Ю. А. ia_ste@mail.ru / You can also contact the authors of the report, or with the head of the scientific group Stepchenkov Ya. A. ia_ste@mail.ru.

Delay-Insensitive Floating Point Multiply-Add-Subtract Unit

I.A. Sokolov, Y.V. Rogdestvenski, Y.G. Diachenko, Y.A. Stepchenkov, N.V. Morozov, D.Y. Stepchenkov, D.Y. Diachenko. Delay-Insensitive Floating Point Multiply-Add-Subtract Unit / Problems of Advanced Micro- and Nanoelektronic Systems Development – 2019, Issue III, Moscow, IPPM RAS, P. 20-25. (is indexed in Scopus).

DOI: 10.31114/2078-7707-2019-3-20-25

Abstract: The subject of this paper is a floating point unit implementing fused multiply-add-subtract operation. It be-longs to the delay-insensitive self-timed (ST) circuits which do not depend on delays both in cells and on wires. It is fully compliant with IEEE 754 Standard and processes both a sum and difference between product of first two operands and third operand. Each 64-bit input operand contains either one double precision number, or two single precision numbers. Thus presented unit calculates either one operation with double precision numbers, or two simultaneous operations with single precision numbers. Multiplier utilizes modified Booth algorithm. In order to increase its performance, it is divided into two pipeline stages with accelerated forced switching to spacer phase. Booth encoder circuit is integrated into an input FIFO. FIFO is implemented as a register file with an output multiplexer and read/write address counters. Using ternary redundant ST code for multiplying, adding and subtracting provides reduction of unit’s complexity. Indication subcircuit considers the constrains imposed by an isochronous area for chosen fabrication technology. For de-creasing energy consumption, the fused multiply-add-subtract unit implements one-channel pipeline. The unit is designed for 65-nm CMOS bulk technology using an indus-trial standard cell library supplemented by self-timed cells. It provides 3 Gflops performance and 2.9-ns latency.

Синтез самосинхронных схем в базисе БМК

Л.П. Плеханов, А.Н. Денисов, Ю.Г. Дьяченко, Ю.А. Степченков, Д.И. Мамонов, Д.Ю. Степченков. Синтез самосинхронных схем в базисе БМК // Научная конференция «Микроэлектроника – ЭКБ и электронные модули». Алушта (Республика Крым), 30.09-05.10.2019. М: Техносфера, 2019. С. 450-454.

DOI: 10.22184/1993-8578.2020.13.3s.460.470

Аннотация: Данный доклад посвящен разработке средств автоматизированного синтеза самосинхронных (CC) схем. Рассматриваются особенности реализации СС-схем. Предложен маршрут проектирования цифровых СС СБИС. Описана интеграция разрабатываемых средств в стандартную САПР синхронных СБИС («Ковчег»), обеспечивающая эффективное проектирование действительно СС-схем.

Abstract: This report is devoted to the development of software for automated synthesis of the self-timed (ST) circuits. Peculiarities of the ST circuit implementation have been discussed, and digital ST VLSI design flow has been offered. Besides, the report highlights an integration of the suggested tools into standard synchronous VLSI CAD (“Kovcheg”), which provides the effective design of real ST circuits.

Advanced Indication of the Self-Timed Circuits

Yuri Stepchenkov, Yuri Diachenko, Yury Rogdestvenski, Yury Shikunov and Denis Diachenko. Advanced Indication of the Self-Timed Circuits // 2019 IEEE EAST-WEST DESIGN & TEST SYMPOSIUM Batumi, Georgia, September 13 — 16, 2019.

Abstract: Paper discusses a problem of the CMOS self-timed circuits’ indication. Large number of indicating signals in the multi-bit computational devices and registers requires an additional hardware and time for their combining and forming a single control signal that provides a request-acknowledge interaction between interconnected self-timed functional blocks. Indication subcircuit performs this. Multi-input hysteretic triggers allows for accelerating indication subcircuit by factor of 1.1 – 1.6 and reducing its complexity in several times in comparison to standard implementation basis on static and semi-static Muller’s elements. A penalty for this is some shortcircuit current in the worst case.

Дополнительную информацию о содержании доклада вы можете получить на сайте конференции / You can get additional information on the content of the article on the conference website. Также вы можете связаться с авторами доклада, или с руководителем научной группы Степченковым Ю. А. ia_ste@mail.ru / You can also contact the authors of the report, or with the head of the scientific group Stepchenkov Ya. A. ia_ste@mail.ru.

Energy Efficient Speed-Independent 64-bit Fused Multiply-Add Unit

Yury Stepchenkov, Yury Rogdestvenski , Yury Diachenko, Dmitry Stepchenkov, Yury Shikunov. Energy Efficient Speed-Independent 64-bit Fused Multiply-Add Unit // 2019 IEEE Conference of Russian Young Researchers in Electrical and Electronic Engineering (EIConRus) Moscow, Russia, January 28-31, 2019. — IEEE, P. 1709 — 1714. (indexed in Scopus).

DOI: 10.1109/EIConRus.2019.8657207.

Abstact: The results of a Speed-Independent Fused Multiply-Add (SIFMA) unit pipeline implementation research are presented. SIFMA is compliant with IEEE 754 Standard. A criterion of the SIFMA pipeline’s maximum performance is formulated. A method of reducing hardware costs of SIFMA multiplier by 1.5-2 times depending on its features is offered. The multiplier utilizes a modified Booth algorithm using self-timed redundant code. A new energy efficient self-timed organization of an input and output FIFO was developed. It provides less complexity versus a previous SIFMA implementation on base of semi-dense register.

Аннотация: В статье изложены результаты исследования конвейерной реализации независимого от задержек устройства умножения-сложения (SIFMA — Speed-Independed Fused Multiply-Add), соответствующего стандарту IEEE 754. Сформулирован критерий максимальной производительности конвейера SIFMA. Предложен способ снижения аппаратных затрат блока умножения в 1.5 – 2 раза (в зависимости от варианта исполнения), выполненного по модифицированному алгоритму Бута с использованием самосинхронного избыточного кода. Разработана новая энергоэффективная самосинхронная организация входного и выходного FIFO с меньшими аппаратными затратами по сравнению с предыдущей реализацией SIFMA. Использование адаптивной индикации в пределах эквихронной зоны позволило снизить на 20% аппаратные затраты на подсхему индикации SIFMA и уменьшить ее задержку на 18%.

Дополнительную информацию о содержании доклада вы можете получить на сайте конференции/ You can get additional information on the content of the article on the conference website. Также вы можете связаться с авторами доклада, или с руководителем научной группы Степченковым Ю. А. ia_ste@mail.ru / You can also contact the authors of the report, or with the head of the scientific group Stepchenkov Ya. A. ia_ste@mail.ru.

Нечувствительный к задержкам блок умножения-сложения-вычитания с плавающей точкой

Соколов И.А., Ю.В. Рождественский, Ю.Г. Дьяченко, Ю.А. Степченков, Н.В. Морозов, Д.Ю. Степченков. Нечувствительный к задержкам блок умножения-сложения-вычитания с плавающей точкой // Проблемы разработки перспективных микро- и наноэлектронных систем – 2018. Сборник трудов / под общ. ред. академика РАН А.Л. Стемпковского. М.: ИППМ РАН, 2018. Часть II. С. 170–177.

DOI: 10.31114/2078-7707-2018-2-170-177

Аннотация: Представлено устройство совмещенного умножения-сложения-вычитания, независящее от задержек в элементах и проводниках. Оно полностью соответствует стандарту IEEE 754 и реализует одновременно операции сложения и вычитания третьего операнда из произведения первых двух. Каждый 64-разрядный операнд содержит либо одно число двойной точности, либо два числа одинарной точности. Для увеличения быстродействия умножитель, реализующий модифицированный алгоритм Бута, разбит на две ступени конвейера с ускоренным переключением в спейсер. Схема кодера Бута интегрирована во входное FIFO. Выполнение сложения и вычитания в троичном избыточном коде обеспечивает сокращение аппаратных затрат всего блока. С целью сокращения энергопотребления блок построен как одноканальное устройство. Блок разработан на базе объемной КМОП технологии с проектными нормами 65 нм с использованием библиотеки стандартных элементов, дополненной самосинхронными элементами, и обеспечивает производительность на уровне 3 гигафлопс.

Self-Timed Floating Point Multiply-Add Unit

Y.A. Stepchenkov, Y.V. Rogdestvenski, Y.G. Diachenko, N.V. Morozov, D.Y. Stepchenkov, B.A. Stepanov, D.Y. Diachenko, A.V. Rogdestvenskene. Self-Timed Floating Point Multiply-Add Unit // Problems of Advanced Micro- and Nanoelectronic Systems Development, 2017, Part III, Moscow, IPPM RAS, P. 45-51. (is indexed in Scopus).

Abstract: The subject of this paper is a Speed-Independent Floating Point Coprocessor (SIFPC) implementing Fused Multiply-Add-Subtract operation. It utilizes mixed dual-rail and redundant self-timed coding, and is compliant with IEEE 754 Standard. SIFPC processes either one operation with double precision numbers, or two simultaneous opera-tions with single precision numbers, and calculates two re-sults: sum and difference between product of first two oper-ands and third operand. SIFPC consists of two identical channels with common input and output. An order of data outputting matches the order of an input data. Each channel implements full data processing path and has two pipeline stages: first is multiplier and exponent calculation, and se-cond is all rest parts. This reduces hardware complexity and accelerates calculations due to reducing number of interme-diate registers and cutting number of «bottlenecks» in an indication subcircuit of the unit. An additional speed-up of performance, comparing to a traditional self-timed circuit implementation, is achieved due to utilizing bit-wise and simplified (adaptive) indication. Multiplier utilizes modified Booth algorithm with Wallace tree, self-timed redundant code and ternary adders. First stage of the Wallace tree compresses four dual-rail partial products into two ternary operands. The unit is designed for standard 65-nm CMOS process. It has 1.12 mm2 die size, demonstrates 3.15 Gflops performance and 1.8 ns latency.

Самосинхронное устройство умножения-сложения с плавающей точкой

Ю.А. Степченков, Ю.В. Рождественский, Ю.Г. Дьяченко, Н.В. Морозов, Д.Ю. Степченков, Б.А.Степанов, Д.Ю. Дьяченко, А.В. Рождественскене. Самосинхронное устройство умножения-сложения с плавающей точкой // Проблемы разработки перспективных микро- и наноэлектронных систем — 2016. Сборник трудов / под общ. ред. академика РАН А.Л. Стемпковского. М.: ИППМ РАН, 2016. Часть III. С. 149- 156.

Аннотация: Представлено самосинхронное устройство совмещенного умножения-сложения в качестве сопроцессора, относящееся к новому подклассу независящих от задержек схем с адаптивной индикацией. Оно полностью соответствует стандарту IEEE 754 и реализует одновременно операции сложения и вычитания третьего операнда из произведения первых двух. Каждый 64-разрядный операнд содержит либо одно число двойной точности, либо два числа одинарной точности. Для минимизации аппаратных затрат и энергопотребления число ступеней конвейера сокращено до двух. Оптимальное соотношение «производительность / аппа-ратные затраты» достигается за счет двух параллельных каналов с общим входом и выходом. Дополнительное сокращение аппаратных затрат и повышение быстро-действия обеспечивается использованием адаптивной индикации. Умножение реализовано на основе самосинхронного избыточного кода. Устройство разработано на базе объемной КМОП технологии с проектными норма-ми 65 нм и обеспечивает производительность на уровне 3,15 гигафлопс.

Speed-Independent Fused Multiply Add and Subtract Unit

Yuri Stepchenkov, Victor Zakharov, Yuri Rogdestvenski, Yuri Diachenko, Nikolai Morozov and Dmitri Stepchenkov. Speed-Independent Fused Multiply Add and Subtract Unit // Proceedings of IEEE East-West Design & Test Symposium (EWDTS’2016), Yerevan, October, 14 — 17, 2016. P. 150-153. (is indexed in Scopus).

DOI: 10.1109/EWDTS.2016.7807735

Abstract: Speed-independent fused multiply-add-subtract unit is offered together with test environment providing full verification of its performance and workability in all range of the environment conditions. It complies with IEEE 754 Standard, and performs double and single precision operations at three operands. The unit is implemented as a two-channel with a common input and output. Each channel is a pipeline with four stages. Multiplier is implemented on the modified Booth algorithm using self-timed redundant code. The unit was designed on a base of standard CMOS process with 65 nm design rules and has 3.15 Gigaflops performance and less than 2 ns latency.

Аннотация: Представлено speed-independent устройство умножения-сложения-вычитания с тестовым окружением, обеспечивающим всестороннюю проверку его характеристик и работоспособности во всем диапазоне условий окружающей среды. Оно соответствует стандарту IEEE 754 и выполняет операции двойной и одинарной точности над тремя операндами. Устройство реализовано как двухканальное с общим входом и выходом. Каждый канал является конвейером с четырьмя стадиями. Умножитель реализован по модифицированному алгоритму Бута с использованием самосинхронного избыточного кода. Устройство разработано на основе КМОП-технологии с проектными нормами 65 нм и обеспечивает производительность на уровне 3.15 гигафлопс и латентность менее 2 нС.

Дополнительную информацию о содержании доклада вы можете получить на сайте конференции / You can get additional information on the content of the article on the conference website. Также вы можете связаться с авторами доклада, или с руководителем научной группы Степченковым Ю. А. ia_ste@mail.ru / You can also contact the authors of the report, or with the head of the scientific group Stepchenkov Ya. A. ia_ste@mail.ru.

Challenges of the Algorithms Optimization and High Performance Arithmetic Coprocessors Development for Numerical Modeling of Gas Flow and Heat Transfer in the Combustion Problem

Sergey Aryashev, Sergey Bobkov, Pavel Zubkovskiy, Eugene Ivasyuk and Yuri Stepchenkov. Challenges of the Algorithms Optimization and High Performance Arithmetic Coprocessors Development for Numerical Modeling of Gas Flow and Heat Transfer in the Combustion Problem // International Conference Of Numerical Analysis And Applied Mathematics 2015 (ICNAAM 2015), Rhodes, Greece, September 22 — 28, 2015. Volume number: 1738, Published: 08 June 2016 P. 220008-1 — 220008-4. (indexed in Web of Science).

DOI: 10.1063/1.4952007.

Abstract: Computer simulation of multiscale burning and detonation processes requires an exaflop-scale performance supercomputer. The paper present research from SRISA intended to development high-performance architectures of DSP extensions for burning process simulations. Also a number of solutions for dataflow coprocessor development based on self-timed circuits are proposed.

Self-timed multiplier for multiply-add unit

B. Stepanov, Y. Diachenko, Y. Rogdestvenski, D. Diachenko. Self-timed multiplier for multiply-add unit // // 2016 IEEE Conference of Russian Young Researchers in Electrical and Electronic Engineering (EIConRus) St. Petersburg, Russia, February 02-03, 2016. — IEEE, P 373-376. (indexed in Scopus).

DOI: 10.1109/EIConRusNW.2016.7448190

Abstract: Paper discusses the peculiarities of self-timed multiplier implementation for unit multiplying two operands and then adding the product to third operand without an intermediate rounding according to the IEEE 754 Standard. The multiplier is a hardware implementation of modified Booth algorithm on a base of self-timed adder with redundant signal code. An optimal self-timed redundant coding of internal and output signals in the multiplier was proposed. The circuitry and layout problems were solved for self-timed multiplier implementation. Wallace tree structure, which is the main part of the multiplier, was optimized for the facilities of 65-nm CMOS process with six metal layers taking into account more number of signals in the multiplier circuit, than in the synchronous analog. A release of the self-timed multiplier implementation in CMOS process with 65-nm design rules is introduced.

Аннотация: Доклад посвящен особенностям реализации самосинхронного умножителя для устройства, выполняющего операцию умножения двух операндов с последующим сложением произведения с третьим операндом без промежуточного округления в соответствии со стандартом IEEE 754. Умножитель является аппаратной реализацией модифицированного алгоритма Бута на основе самосинхронного сумматора с избыточным кодированием сигналов. Предложено оптимальное избыточное самосинхронное кодирование внутренних и выходных сигналов умножителя. Решены проблемы схемотехнической и топологической реализации самосинхронного умножителя. Структура дерева Уоллеса –основной части умножителя, –оптимизирована под возможности 65-нм КМОП технологии с шестью слоями металлизации с учетом большего, чем в синхронном аналоге, количества сигналов в схеме умножителя. Представлена топологическая реализации самосинхронного умножителя в КМОП технологии с проектными нормами 65 нм.

Дополнительную информацию о содержании доклада вы можете получить на сайте конференции / You can get additional information on the content of the article on the conference website. Также вы можете связаться с авторами доклада, или с руководителем научной группы Степченковым Ю. А. ia_ste@mail.ru / You can also contact the authors of the report, or with the head of the scientific group Stepchenkov Ya. A. ia_ste@mail.ru.

Самосинхронный умножитель для распределенных вычислений

Степанов Б.А., Дьяченко Ю.Г., Рождественский Ю.В. Самосинхронный умножитель для распределенных вычислений // Труды Второй молодежной научной конференции «Задачи современной информатики» – М.: ФИЦ ИУ РАН, 2015. – С. 201-207.

Аннотация: Доклад посвящен особенностям реализации самосинхронного умножителя для устройства умножения-сложения. Обоснован выбор оптимального самосинхронного кодирования сигналов умножителя с помощью избыточного троичного самосинхронного кода. Предложена структура дерева Уоллеса – основной части умножителя. Рассматриваются проблемы схемотехнической и топологической реализации умножителя. Представлен вариант реализации самосинхронного умножителя в КМОП технологии с проектными нормами 65 нм.

Библиотека функциональных ячеек для самосинхронных БМК-СБИС

Степченков Ю.А., Денисов А.Н., Дьяченко Ю.Г., Гаврилов С.В., Морозов Н.В., Степченков Д.Ю. Библиотека функциональных ячеек для самосинхронных БМК-СБИС / М.: Техносфера. Международная конференция «Микроэлектроника 2015» Интегральные схемы и микроэлектронные модули: проектирование, производство и применение. Сборник тезисов. Крым, г. Алушта, 28 сентября – 3 октября 2015 г. 9 С. 220-228, 2016.

Аннотация: Данный доклад посвящен разработке средств проектирования и изготовления самосинхронных (CC) СБИС (всех возможных классов) на основе базовых матричных кристаллов (БМК). Обосновывается выбор БМК, как базиса для проектирования СС-БИС. Описывается состав библиотеки функциональных ячеек, обеспечивающих эффективное проектирование СС-схем различных классов на базе отечественной серии БМК 5503/5507, 5521/5528.

Abstract: This report is devoted to development of design tools and production of self-timed (ST) VLSI (all possibleclasses) on the basis of the gate arrays (GA). GA choice, as basis for design of SS-VLSIlocates. The structure of libraryof the elements providing effective design of SS-circuits of various classes on the basis of the GA 5503/5507, 5521/5528domestic series is described.

Functional Approach in Self-timed Circuits Design

Plekhanov Leonid, Zakharov Victor and Stepchenkov Yuri. Functional Approach in Self-timed Circuits Design // Proceedings of IEEE East-West Design & Test Symposium (EWDTS’2015), Batumi, Georgia, September 26 — 29, 2015. P. 282-285. (indexed in Scopus).

Abstract: Self-timed circuits have the unique properties of a lack of competition. One of the main problems of such circuits design — the analysis on self-timing (elements switching) and the construction of large circuits. In traditional approach computational complexity is so great, that it does not allow to analyze the most important practical circuits. In the functional approach we propose hierarchical method: on the lower level logic functions of elements are analyzed, on the top — the relationships between blocks. The complexity of calculations here is close to the linear function of the size of circuit. Such approach solves one of the main problems of self-timed circuits design — analysis circuits of any size. The efficiency of the proposed methods was confirmed by the developed SW.

Аннотация: Самосинхронные схемы (не зависящие от задержек элементов) имеют уникальные свойства отсутствия состязаний и отказобезопасности. Одна из главных проблем проектирования таких схем – анализ самосинхронности и построение больших схем. В традиционном подходе – анализе переключений элементов – сложность вычислений столь велика, что не позволяет анализировать большинство практически значимых схем. В функциональном подходе предлагается иерархический метод: на нижнем уровне анализируются логические функции элементов, на верхних — взаимосвязи блоков. Трудоёмкость вычислений здесь близка к линейной от размера схемы. Такой подход решает одну из главных проблем проектирования самосинхронных схем – анализ и построение схем любого размера. Эффективность предложенных методов подтверждена с помощью разработанных программных средств.

Дополнительную информацию о содержании доклада вы можете получить на сайте конференции / You can get additional information on the content of the article on the conference website. Также вы можете связаться с авторами доклада, или с руководителем научной группы Степченковым Ю. А. ia_ste@mail.ru / You can also contact the authors of the report, or with the head of the scientific group Stepchenkov Ya. A. ia_ste@mail.ru.

Cell Library for Speed-Independent VLSI

Stepchenkov Yuri, Zakharov Victor, Diachenko Yuri, Morozov Nickolaj and Stepchenkov Dmitri. Cell Library for Speed-Independent VLSI // Proceedings of IEEE East-West Design & Test Symposium (EWDTS’2015), Batumi, Georgia, September 26 — 29, 2015. P. 137-140. (indexed in Scopus).

Abstract: Paper describes content and implementation features of the cell library intended for digital self- timed (speed-independent) circuit design. The library contains more than 200 cells. Self-timed triggers with unary input and triggers with forced output are presented. The library was certified by means of developed characterization tool and was practically tested in a set of digital signal processing units manufactured in differential CMOS processes.

Аннотация: Описаны состав и особенности реализации библиотеки элементов для проектирования цифровых самосинхронных (не зависящих от задержек элементов) схем. Библиотека содержит более 200 элементов, в том числе, самосинхронные триггеры с унарным информационным входом и усиленным выходом и аттестована с помощью разработанной программы характеризации и прошла практическую апробацию в ряде изготовленных микросхем цифровой обработки данных с различными технологическими нормами.

Дополнительную информацию о содержании доклада вы можете получить на сайте конференции/ You can get additional information on the content of the article on the conference website. Также вы можете связаться с авторами доклада, или с руководителем научной группы Степченковым Ю. А. ia_ste@mail.ru / You can also contact the authors of the report, or with the head of the scientific group Stepchenkov Ya. A. ia_ste@mail.ru.

Speed-Independent Floating Point Coprocessor

Stepchenkov Yuri, Zakharov Victor, Rogdestvenski Yuri, Diachenko Yuri, Morozov Nickolaj and Stepchenkov Dmitri. Speed-Independent Floating Point Coprocessor // Proceedings of IEEE East-West Design & Test Symposium (EWDTS’2015), Batumi, Georgia, September 26 — 29, 2015. P. 111-114. (indexed in Scopus).

Abstract: Speed-independent fused multiply-add unit as a coprocessor is represented. It purely conforms to IEEE 754 Standard. For minimization hardware and power consumption, a number of pipeline stages is reduced down to two. Wallace tree in the multiplier utilizes redundant self-timed code. Represented unit is developed on a base of standard 65-nm CMOS bulk process. It provides a performance up to 0.54 Gflops, and power consumption at level of 450 mW/Gflops.

Аннотация: Представлено speed-independent устройство совмещенного умножения-сложения в качестве сопроцессора. Оно полностью соответствует стандарту IEEE 754. Для минимизации аппаратурных затрат и энергопотребления число ступеней конвейера сокращено до двух. Дерево Уоллеса в умножителе реализовано с использованием самосинхронного избыточного кода . Устройство разработано на основе объемной КМОП-технологии с проектными нормами 65 нм и обеспечивает производительность на уровне 0.54 гигафлопс. Энергопотребление устройства равно примерно 450 мВт/Гфлопс.

Дополнительную информацию о содержании доклада вы можете получить на сайте конференции / You can get additional information on the content of the article on the conference website. Также вы можете связаться с авторами доклада, или с руководителем научной группы Степченковым Ю. А. ia_ste@mail.ru / You can also contact the authors of the report, or with the head of the scientific group Stepchenkov Ya. A. ia_ste@mail.ru.

Использование самосинхронной логики для снижения потребляемой мощности и повышения надёжности микропроцессоров

Бобков С.Г., Горбунов М.С., Дьяченко Ю.Г., Рождественский Ю.В., Степченков Ю.А., Сурков А.В. Использование самосинхронной логики для снижения потребляемой мощности и повышения надёжности микропроцессоров // Проблемы разработки перспективных микро- и наноэлектронных систем — 2014. Сборник трудов / под общ. ред. академика РАН А.Л. Стемпковского. М.: ИППМ РАН, 2014. Часть I. С. 43-48.

Bobkov S.G., Gorbunov M.S., Diachenko Yu.G., Rozhdestvenskij Yu.V., Stepchenkov Yu.A., Surkov A.V. Delay Insensitive Circuits for Low Power and Highly Reliable Microprocessors // Problems of Advanced Micro- and Nanoelectronic Systems Development, 2015, Part I, Moscow, IPPM RAS, P. 12-13.

Bobkov S.G., Gorbunov M.S., Diachenko Yu.G., Rozhdestvenskij Yu.V., Stepchenkov Yu.A., Surkov A.V. Delay Insensitive Circuits for Low Power and Highly Reliable Microprocessors // Problems of Perspective Micro- and Nanoelectronic Systems Development — 2014. Proceedings / edited by A. Stempkovsky, Moscow, IPPM RAS, 2014. Part I. P. 43-48.

Аннотация: В статье дается обоснование использования самосинхронной логики с целью повышения надежности и снижения потребляемой мощности микропроцессорных систем.

Abstract: The article shows that delay insensitive circuits can increase the reliability and decrease the power consumption of microprocessor systems.

Самосинхронное устройство умножения-сложения гигафлопсного класса: методологические аспекты

Соколов И.А., Степченков Ю.А., Рождественский Ю.В., Дьяченко Ю.Г. Самосинхронное устройство умножения-сложения гигафлопсного класса: методологические аспекты // Проблемы разработки перспективных микро- и наноэлектронных систем — 2014. Сборник трудов / под общ. ред. академика РАН А.Л. Стемпковского. М.: ИППМ РАН, 2014. Часть IV. С. 51-56.

Sokolov I.A., Stepchenkov Yu.A., Rozhdestvenskij Yu.V., Diachenko Yu.G. Speed-Independent Fused Multiply-Add Unit of Gigaflops Rating: Methodological Aspects // Problems of Advanced Micro- and Nanoelectronic Systems Development, 2015, Part IV, Moscow, IPPM RAS, P. 13-14.

Sokolov I.A., Stepchenkov Yu.A., Rozhdestvenskij Yu.V., Diachenko Yu.G. Speed-Independent Fused Multiply-Add Unit of Gigaflops Rating: Methodological Aspects // Problems of Perspective Micro- and Nanoelectronic Systems Development — 2014. Proceedings / edited by A. Stempkovsky, Moscow, IPPM RAS, 2014. Part IV. P. 51-56.

Аннотация: Представлены подходы к проектированию самосинхронной (СС) аппаратуры и рассмотрены условия внутрисистемной интеграции синхронных и СС-устройств в рамках супер-ЭВМ на примере разработки СС-устройства умножения-сложения гигафлопсного класса, соответствующего стандарту IEEE 754 и выполняющего либо одну операцию двойной точности, либо одновременно две операции одинарной точности над входными операндами. Устройство реализовано по КМОП-технологии с проектными нормами 65 нм. В зависимости от исполнения, оно работает с асинхронным или синхронным окружением и обеспечивает производительность на уровне не менее 1 гигафлопс при времени задержки формирования результата относительно поступления входных операндов не более 6 нС.

Abstract: This report contains the approaches to designing self-timed (ST) hardware and discusses the requirements for in-system integration of the synchronous and ST units in a framework of supercomputer by an example of development of Speed-Independed Fused Multiply-Add (SIFMA) unit of gigaflops rating conforming to IEEE 754 Standard. SIFMA performs either one double precision operation, or two simultaneous single precision operations with input operands. SIFMA was designed under industrial CMOS 65-nm technology. Depending on implementation, it operates with synchronous or asynchronous environment and provides performance no less than 1 Gigaflops at latency up to 6 ns.

Самосинхронное устройство умножения-сложения гигафлопсного класса: варианты реализации

Степченков Ю.А., Рождественский Ю.В., Дьяченко Ю.Г., Морозов Н.В., Степченков Д.Ю., Сурков А.В. Самосинхронное устройство умножения-сложения гигафлопсного класса: варианты реализации // Проблемы разработки перспективных микро- и наноэлектронных систем — 2014. Сборник трудов / под общ. ред. академика РАН А.Л. Стемпковского. М.: ИППМ РАН, 2014. Часть IV. С. 57-60.

Stepchenkov Yu.A., Rozhdestvenskij Yu.V., Diachenko Yu.G., Morozov N.V., Stepchenkov D.Yu., Surkov A.V. Speed-Independent Fused Multiply-Add Unit of Gigaflops Rating: Implementation Variants // Problems of Advanced Micro- and Nanoelectronic Systems Development, 2015, Part IV, Moscow, IPPM RAS, P. 15-16.

Stepchenkov Yu.A., Rozhdestvenskij Yu.V., Diachenko Yu.G., Morozov N.V., Stepchenkov D.Yu., Surkov A.V. Speed-Independent Fused Multiply-Add Unit of Gigaflops Rating: Implementation Variants // Problems of Perspective Micro- and Nanoelectronic Systems Development — 2014. Proceedings / edited by A. Stempkovsky, Moscow, IPPM RAS, 2014. Part IV. P. 57-60.

Аннотация: В докладе изложены результаты разработки вариантов независимого от задержек устройства умножения-сложения (SIFMA – Speed-Independed Fused Multiply-Add), соответствующего стандарту IEEE 754 и выполняющего либо одну операцию двойной точности, либо одновременно две операции одинарной точности над тремя операндами. Устройство разработано по стандартной КМОП технологии с проектными нормами 65 нм. Оно работает с синхронным или асинхронным окружением и обеспечивает производительность на уровне 1 гигафлопс при напряжении питания 1 В и температуре 25 градусов Цельсия. Энергопотребление при этом не превышает 9710 мДж/ГГц.

Abstract: This report contains the results of development of two variants of Speed-Independed Fused Multiply-Add (SIFMA) conforming to IEEE 754 Standard. SIFMA performs either one double precision operation, or two simultaneous single precision operations with three operands. SIFMA was designed under industrial CMOS 65-nm technology. It operates with synchronous and asynchronous environments and provides performance up to 1 Gigaflops at 1.0 volt of supply voltage and 25 Celsius degrees. At this, power efficiency does not exceed 970 mJ/GHz.

Самосинхронный базис реализации радиационностойких микросхем

Бобков С. Г., Степченков Ю. А., Плеханов Л. П., Дьяченко Ю. Г., Сурков А. В. Самосинхронный базис реализации радиационностойких микросхем // Труды 1-й российско-белорусской научно-технической конференции «Элементная база отечественной радиоэлектроники», посвящённой 110-летию со дня рождения О. В. Лосева / Под ред. А. Э. Рассадина. ‑ Н. Новгород.: НИЖЕГОРОДСКАЯ РАДИОЛАБОРАТОРИЯ. 2013. Т. 2. С. 31-35.

Аннотация: В последние годы неуклонное развитие технологий и растущие требования выявляют все больше, встающих перед разработчиками задач: снижение энергопотребления при увеличении производительности, повышение надежности и помехозащищенности схем. Поиск решений этих проблем возродил интерес к независимой от задержек схемотехнике (НЗ-cхемотехнике), имеющей важные преимущества перед синхронными схемами.

Полузаказная библиотека самосинхронных элементов для ответственных применений

Денисов А.Н., Степченков Ю.А., Дьяченко Ю.Г., Плеханов Л.П., Филимоненко О.П.Полузаказная библиотека самосинхронных элементов для ответственных применений // Первая российско-белорусская научно-техническая конференция «Элементная база отечественной радиоэлектроники», т. 2, Нижний Новгород, 2013. С. 35-39.

Аннотация: Проблемы создания отечественной элементной компонентной базы (ЭКБ) общеизвестны, но в ответственных приложениях, таких как космическое приборостроение, они становятся одним из определяющих факторов. ЭКБ для применения в естественных условиях космического пространства – отдельный класс элементной базы, со своими отдельными требованиями, главными из которых являются стойкость к накопленной дозе радиационного излучения, защищенность от тиристорного эффекта, минимизация энергопотребления и повышенная надежность.

Асинхронные микропроцессоры для космических систем микросхем

Бобков С.Г., Сурков А.В., Степченков Ю.А., Дьяченко Ю.Г. Асинхронные микропроцессоры для космических систем микросхем // Труды 1-й российско-белорусской научно-технической конференции «Элементная база отечественной радиоэлектроники», посвящённой 110-летию со дня рождения О. В. Лосева / Под ред. А. Э. Рассадина. ‑ Н. Новгород.: НИЖЕГОРОДСКАЯ РАДИОЛАБОРАТОРИЯ. 2013. Т. 2. С. 27-31.

Bobkov S.G., Surkov A.V., Stepchenkov Yu.A., Dyachenko Yu.G. Asynchronous microprocessors for space systems //Works of the 1st Russian-Belarusian scientific and technical conference «Element Base of Domestic Radio Electronics» devoted by 110th since the birth of O. V. Losev / Under the editorship of. A.E.Rassadina. — N Novgorod. : NIZHNY NOVGOROD RADIO LABORATORY. 2013 . T. 2 . Page 27-31.

Аннотация: Естественная надежность асинхронных схем и пониженное потребление позволили им занять свою нишу в классе микросхем для специальных применений. В первую очередь эти микросхемы используются для смарт-карт с жёсткими требованиями по потреблению и питанию. В области защиты информации и криптографии асинхронные схемы популярны в силу невозможности взлома алгоритмов по анализу спектра потребления. В сигнальных процессорах низкая шумность питания асинхронных схем позволила не только совмещать цифровую и аналоговую часть на одном кристалле, но и существенно повысить точность измерений. В космических применениях асинхронные схемы проявили себя особенно широко.

Функциональный метод анализа самосинхронных схем любого размера

Плеханов Л.П. Функциональный метод анализа самосинхронных схем любого размера // Проблемы разработки перспективных микро- и наноэлектронных систем — 2012. Сборник трудов / под общ. ред. академика РАН А.Л. Стемпковского. М.: ИППМ РАН, 2012. С. 107-112.

Plekhanov L.P. The Functional Method of the Analysis of Speed-Independent Circuits of Any Size // Problems of Perspective Micro- and Nanoelectronic Systems Development — 2012. Proceedings / edited by A. Stempkovsky, Moscow, IPPM RAS, 2012. P. 107-112.

Аннотация: Развитию и внедрению самосинхронных схем, обладающих уникальными свойствами, во многом препятствуют трудности проектирования, в частности ‑ анализ на самосинхронность «больших» схем. В докладе предлагается метод анализа схем неограниченного размера, основанный на функциональном подходе. В литературе подобного подхода не отмечено, и метод здесь приводится впервые.

Abstract: Development and implementation of the speed-independent circuits, possessing unique properties, are largely discouraged by design difficulties, in particular, the analysis for speed-independence of «large» circuits. In the report it is suggested the method of the analysis of circuits of unlimited size, based on the functional approach. In the literature, this approach is not observed, and a method is provided here for the first time.

Проектирование самосинхронных схем: функциональный подход

Плеханов Л.П. Проектирование самосинхронных схем: функциональный подход // Проблемы разработки перспективных микро- и наноэлектронных систем — 2010. Сборник трудов / под общ. ред. академика А.Л.Стемпковского. М.:ИППМ РАН, 2010. С. 424-429.

Plekhanov L.P. Design of Self-Timed Circuits: a Functional Approach // Problems of Perspective Micro- and Nanoelectronic Systems Development — 2010. Proceedings / edited by A. Stempkovsky, Moscow, IPPM RAS, 2010. P. 424-429.

Аннотация: Предложен новый подход к проектированию уникальных по свойствам самосинхронных схем. Подход призван приблизить проектирование этих схем к категориям и понятиям, привычным для большинства разработчиков, без использования методов теории автоматов. В рамках подхода эффективно решена задача анализа самосинхронных схем и некоторые задачи синтеза. Подход открывает новые возможности в проектировании таких схем, трудно реализуемые в существующих событийных методах: иерархический анализ, иерархический синтез, покрытие широкого класса неисправностей.

Abstract: A new approach to design of speed-independent (SI) circuits having unique properties is proposed. The approach is called to bring the design of these circuits nearer to the categories and notions usual for most designers, without methods of automata theory. With the approach an analysis task of SI-circuits is effectively solved and also some synthesis tasks are solved. The approach opens new potentialities for the design flow inaccessible to existing eventbased methods: hierarchical analysis, hierarchical synthesis, coverage of large fault class.

Подсистема событийного анализа самосинхронных схем АСПЕКТ

Рождественский Ю.В., Морозов Н.В., Рождественскене А.В. Подсистема событийного анализа самосинхронных схем АСПЕКТ // Проблемы разработки перспективных микро- и наноэлектронных систем — 2010. Сборник трудов / под общ. ред. академика А.Л.Стемпковского. М.:ИППМ РАН, 2010. С. 26-31.

Rozhdestvenskij Yu.V., Morozov N.V., Rozhdestvenskene A.V. ASPECT – a Subsystem of Event Analysis of Self-Timed Circuits // Problems of Perspective Micro- and Nanoelectronic Systems Development — 2010. Proceedings / edited by A. Stempkovsky, Moscow, IPPM RAS, 2010. P. 26-31

Аннотация: Предметом доклада является метод анализа асинхронных схем на независимость их поведения от задержек логических элементов, построенный на событийных моделях функционирования электронных схем. Схема определяется системой булевых уравнений, удовлетворяющей гипотезе Маллера относительно задержек логических элементов. Предлагаемый метод в теоретической части базируется на диаграммах переходов (метод в глобальных состояниях) с последующим тождественным преобразованием к событийным моделям. Полученные алгоритмы анализа обладают строгой фундаментальностью метода в глобальных состояниях, но не требует полного перебора достижимых состояний схемы. Сложность задачи изменилась с экспоненциальной на полиномиальную. Подсистема АСПЕКТ — это комплекс программ, реализующий событийный метод анализа.

Abstract: This report deals with a method of asynchronous circuits analysis examining their functionality independence on gate’s delays. The method is based on event models of circuit’s behavior. A circuit is defined by logic equations satisfying Muller’s hypothesis on delays of logic gates. Suggested method theoretically bases on transition diagrams (in global states) with their following equivalent transforming into the event models. Developed algorithms of analysis have a strict fundamentality of global states method but do not need in full probing of achievable states of a circuit. As a result, task’s complexity became a polynomial instead of an exponential one. Subsystem ASPECT is a software complex implementing an event method of analysis.

Самосинхронный вычислитель для высоконадежных применений

Степченков Ю.А., Дьяченко Ю.Г., Рождественский Ю.В., Морозов Н.В., Степченков Д.Ю. Самосинхронный вычислитель для высоконадежных применений // Проблемы разработки перспективных микро- и наноэлектронных систем — 2010. Сборник трудов / под общ. ред. академика А.Л.Стемпковского. М.:ИППМ РАН, 2010. С. 418-423.

Stepchenkov Yu.A., Diachenko Yu.G., Rozhdestvenskij Yu.V., Morozov N.V., Stepchenkov D.Yu. Self-Timed Computing Device for High-Reliable Applications // Problems of Perspective Micro- and Nanoelectronic Systems Development — 2010. Proceedings / edited by A. Stempkovsky, Moscow, IPPM RAS, 2010. P. 418-423.

Аннотация: Представлены результаты разработки полностью самосинхронного вычислительного блока (в дальнейшем – вычислителя), выполняющего функции деления и извлечения квадратного корня в соответствии со стандартом IEEE 754. Оптимизированная индикаторная подсхема гарантирует стопроцентный контроль окончания переключений всех элементов схемы на каждой фазе работы. Достоверность самосинхронности обеспечивается иерархическим анализом.

Abstract: Design results of self-timed computing device performing division and square root extraction in accordance with IEEE 754 Standard are presented. Advanced indicating subcircuit provides full total-lot control of transition termination of all elements in the computing device at each phase of work. Suggested hierarchical analysis provides a validity of a self-timed feature of the computing device.

Quasi-Delay-Insensitive Computing Device: Methodological Aspects and Practical Implementation

Stepchenkov Y., Diachenko Y., Zakharov V., Rogdestvenski Y., Morozov N., Stepchenkov D. Quasi-Delay-Insensitive Computing Device: Methodological Aspects and Practical Implementation // PATMOS’2009: Proceedings of the International Workshop on power and timing modeling, optimization and simulation. – Delft, The Netherlands, Springer 2010. P. 276–285.

Abstract: The approaches to self-timed hardware design are presented. The conditions of intersystem integration of synchronous and self-timed devices are considered through the example of the quasi-delay-insensitive computing device development. This device performs functions of division and square root extraction. It operates with numbers of single and double precisions corresponding to the IEEE 754 standard.

Характеризация псевдодинамических элементов

Дьяченко Ю.Г., Степченков Д.Ю., Морозов Н.В. Характеризация псевдодинамических элементов // Проблемы разработки перспективных микро- и наноэлектронных систем — 2010. Сборник трудов / под общ. ред. академика А.Л.Стемпковского. М.:ИППМ РАН, 2010. С. 32-35.

Diachenko Yu.G., Stepchenkov D.Yu., Morozov N.V. Characterization of pseudodynamic elements // Problems of Perspective Micro- and Nanoelectronic Systems Development — 2010. Proceedings / edited by A. Stempkovsky, Moscow, IPPM RAS, 2010. P. 32-35.

Аннотация: Представлены результаты апробации процесса характеризации псевдодинамических элементов, составляющих основу схемотехнического базиса самосинхронного (СС) вычислителя, выполняющего операции деления и извлечения квадратного корня в соответствии со стандартом IEEE 754. Описан программный комплекс трансляции результатов характеризации, обеспечивающий формирование стандартных файлов функционально-логического описания библиотечных элементов (БЭ) для вновь вводимых элементов. Эффективность программного комплекса подтверждена при проектировании СС-вычислителя.

Abstract: The experimental results of approbation of pseudodynamic logic elements characterization procedure are presented. These elements form a basis for implementing self-timed computing device, which performs division and square root extraction in accordance with IEEE 754 Standard. A software tool formatting the characterization results is described. It provides generation of conventional files with functional and simulation models for new developed library elements on base of characterization results. An efficiency of suggested software tool is proved while designing self-timed computing device.

Квазисамосинхронный вычислитель: методологические и алгоритмические аспекты

Степченков Ю.А., Дьяченко Ю.Г., Бобков С.Г. Квазисамосинхронный вычислитель: методологические и алгоритмические аспекты // Проблемы разработки перспективных микро- и наноэлектронных систем — 2008. Сборник научных трудов / под общ. ред. А.Л.Стемпковского. М.:ИППМ РАН, 2008. С. 441-446.

Stepchenkov Yu.A., Diachenko Yu.G., Bobkov S.G. Quasi-Delay-Insensitive Computing Device: Methodological and Algorithmic Aspects // Problems of Perspective Micro- and Nanoelectronic Systems Development — 2008. Proceedings / edited by A. Stempkovsky, Moscow, IPPM RAS, 2008. P. 441-446.

Аннотация: Представлены результаты практической разработки квазисамосинхронного вычислительного блока (в дальнейшем – вычислителя), выполняющего функции деления и извлечения квадратного корня в соответствии с алгоритмом, представленным в работе [3]. Обрабатываемыми операндами служат числа одинарной и двойной точности в соответствии со стандартом IEEE 754.

Abstract: The approaches to self-timed hardware design are presented. The conditions of intersystem integration of synchronous and self-timed devices are considered through the example of the quasi-delay-insensitive computing device development. This device performs functions of division and square root extraction. It operates with numbers of single and double precisions corresponding to the IEEE 754 standard.

Квазисамосинхронный вычислитель: практическая реализация