Публикации

Self-timed look up table for ULAs and FPGAs

Tyurin S. F., Skornyakova A. Yu., Stepchenkov Y. A., Diachenko Y. G. Self-timed look up table for ULAs and FPGAs // Radio Electronics, Computer Science, Control, 2021. No 1, P. 36-45.

DOI: 10.15588/1607-3274-2021-1-4

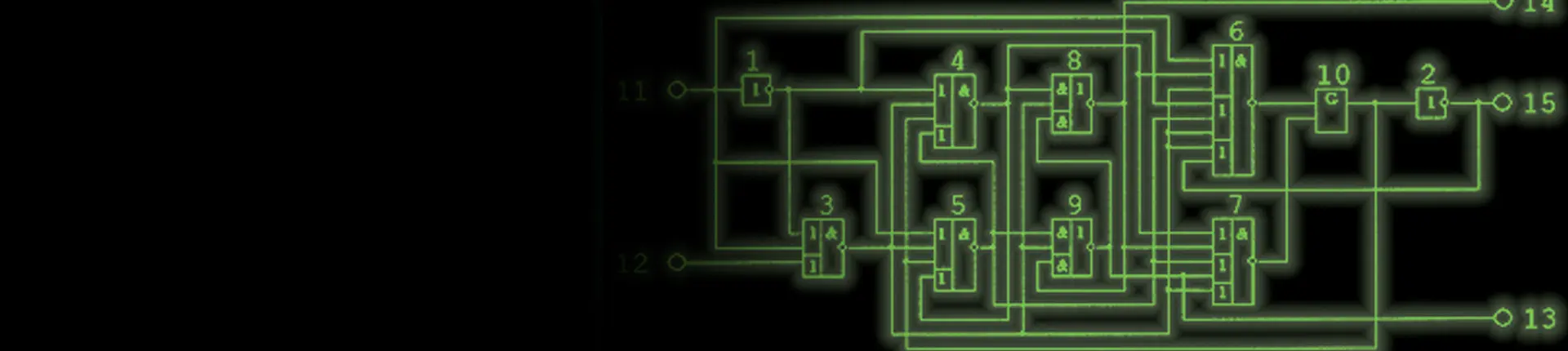

Abstract: Context. Self-Timed Circuits, proposed by D. Muller on the rise of the digital era, continues to excite researchers’ minds. These circuits started with the task of improving performance by taking into account real delays. Then Self-Timed Circuits have moved into the field of green computing. At last, they are currently positioned mainly in the field of fault tolerance. There is much redundancy in Self-Timed Circuits. It is believed that Self-Timed Circuits approaches will be in demand in the nano-circuitry when a synchronous approach becomes impossible. Strictly Self-Timed Circuits check transition process completion for each gate’s output. For this, they use so-called D. Muller elements (C-elements, hysteresis flip-flops, G-flip-flops). Usually, Self-Timed Circuits are designed on Uncommitted Logic Array. Now an extensive base of Uncommitted Logic Array Self-Timed gates exists. It is believed that Self-Timed Circuits are not compatible with FPGA technology. However, attempts to create self-timed FPGAs do not stop. The article proposes a Self-Timed Lookup Table for the Self-Timed Uncommitted Logic Array and the Self-Timed FPGA, carried out either by constants or utilizing additional memory cells. Authors proposed 1,2 – Self-Timed Lookup Table and described simulation results.

Objective. The work’s goal is the analysis and design of the Strictly Self-Timed universal logic element based on Uncommitted Logic Array cells and pass-transistors circuits.

Methods. Analysis and synthesis of the Strictly Self-Timed circuits with Boolean algebra. Simulation of the proposed element in the CAD “ARC”, TRANAL program, system NI Multisim by National Instruments Electronics Workbench Group, and layout design by Microwind. The reliability theory and reliability calculations in PTC Mathcad.

Results. Authors designed, analyzed, and proved the Self-Timed Lookup Table’s workability for the Uncommitted Logic Arrays and FPGAs. Layouts of the novel logic gates are ready for manufacturing.

Conclusions. The conducted studies allow us to use proposed circuits in perspective digital devices.

Аннотация: Актуальность. Самосинхронные схемы, предложенные Д. Маллером на заре цифровой эры, продолжают волновать умы исследователей. Эти схемы стартовали с задач повышения производительности с учетом реальных задержек. Затем самосинхронные схемы перешли в область «зеленых» вычислений и, наконец, в настоящее время позиционируются в основном в области отказоустойчивости. В самосинхронных схемах много избыточности. Считается, что подходы самосинхронных схем будут востребованы в нано-схемотехнике, когда синхронный подход становится невозможным. Строго самосинхронные схемы анализируют окончание переходного процесса на выходах каждого вентиля, используя так называемые элементы Маллера (C-элементы, гистерезисные триггеры, G-триггеры). Обычно самосинхронные схемы разрабатываются для базовых матричных кристаллов. Имеется обширная база самосинхронных схем базовых матричных кристаллов. Считается, что самосинхронные схемы не совместимы с технологией FPGA. Но попытки создания самосинхронных ПЛИС не прекращаются. В статье предлагается строго самосинхронный генератор функций для самосинхронных схем базовых матричных кристаллов и самосинхронных FPGA, конфигурирование которых осуществляется либо константами, либо с помощью дополнительных ячеек памяти. Авторы предложили 1,2 – LUT-самосинхронный и описали результаты моделирования.

Цель. Целью данной работы является анализ и проектирование строго самосинхронного универсального логического элемента LUT, основанного на элементах БМК и на схемах из передающих транзисторов.

Методы. Анализ и синтез строго самосинхронных схем с помощью булевой алгебры. Моделирование предложенного элемента в САПР «Ковчег», программе TRANAL, системах NI Multisim от National Instruments Electronics Workbench Group и топологического проектирования Microwind. Теория надежности и соответствующие расчеты в СКА Mathcad.

Результаты. Авторы разработали, проанализировали и доказали работоспособность самосинхронных генераторов функций для базовых матричных кристаллов и для ПЛИС. Топологии новых логических элементов готовы к изготовлению.

Выводы. Проведенные исследования позволяют использовать предложенные схемы в перспективных цифровых устройствах.

Повышение сбоеустойчивости самосинхронных схем

И. А. Соколов, Ю. А. Степченков, Ю. Г. Дьяченко, Ю. В. Рождественский. Повышение сбоеустойчивости самосинхронных схем // Информатика и Применения, – М.: ТОРУС ПРЕСС, Т. 14, № 4, 2020 – С. 63-68.

DOI: 10.14357/19922264200409

Аннотация: Анализируется проблема устойчивости самосинхронных (СС) схем, изготовленных по технологии комплементарный металл–диэлектрик–полупроводник (КМДП), к кратковременным логическим сбоям (ЛС), генерируемым внешними воздействиями: ядерными частицами, космическими лучами, электромагнитными наводками. Практические СС-схемы реализуются в виде конвейера с запрос-ответным взаимодействием между его ступенями и двухфазной дисциплиной работы с чередованием рабочей фазы и спейсера.Комбинационная часть ступени конвейера использует парафазное со спейсером кодирование информационных сигналов. Индикаторная подсхема ступени конвейера подтверждает окончание переключения всех элементов ступени, возбужденных в текущей фазе работы, и формирует сигналы управления запрос-ответным взаимодействием ступеней конвейера. Рассмотрены физические причины появления ЛС и проанализированы типы сбоев, возможных в КМДП-СС-схемах с проектными нормами 65 нм и ниже. Сравниваются характеристики сбоеустойчивости разных вариантов СС-регистров хранения. Предлагаются схемотехнические и топологические методы повышения сбоеустойчивости СС-конвейера. Даются оценки сбоеустойчивости СС-конвейера в зависимости от места появления ЛС.

Abstract: The paper considers a tolerance of self-timed (ST) circuits fabricated with complementary metal–oxide–semiconductor (CMOS) process to short-term soft errors generated by external causes, namely, nuclear particles, cosmic rays, electromagnetic pulses, and noises. Pipeline implementation is usual for practical ST-circuits. Its control bases on handshake between pipeline stages and two-phase operation discipline with a sequence of the working phase and spacer one. Combinational part of the pipeline stage uses dual-rail information signal coding with a spacer. The pipeline stage indication part acknowledges a switching completion of all stage cells, fired at the current operation phase, and generates handshake signals in ST-pipeline stages control. The paper discusses the physical causes of the short-term soft errors. It analyzes soft error types that may appear in CMOS ST-circuits fabricated with 65-nanometer and below standard bulk process. The tolerance level of the proposed soft error hardened ST-register bits is discussed and compared. The paper suggests circuitry and layout techniques improving ST-pipeline soft error tolerance and estimates soft error immunity level for all pipeline parts depending on soft error location.

Устойчивость самосинхронного конвейера к логическим сбоям в комбинационной части

Степченков Ю. А., Дьяченко Ю. Г., Рождественский Ю. В., Морозов Н. В., Степченков Д. Ю., Дьяченко Д. Ю. Устойчивость самосинхронного конвейера к логическим сбоям в комбинационной части // Системы и средства информатики, 2020. Т. 30. № 3. С. 49-55.

DOI: 10.14357/08696527200305. Индексируется в РИНЦ, ВАК, RSCI.

Аннотация: Оценивается вероятность повреждения данных в самосинхрон- ных (СС) схемах, изготовленных по КМДП-технологии с проектными нормами 65 нм и ниже, из-за кратковременных логических сбоев (ЛС) в комбинационной части ступени СС-конвейера, вызванных внешними и внутренними факторами. Выявлены ситуации, способные привести к порче данных в конвейере из-за ЛС. Определен уровень естественной защищенности СС-кон- вейера от ЛС в его комбинационной части благодаря свойствам СС-схем (84,4% в наихудшем случае). Предложенные приемы топологического синтеза повышают сбоеустойчивость СС-конвейера до 85,6% от всех ЛС. Индикация состояния парафазного сигнала, инверсного по отношению к его спейсеру, как спейсера обеспечивает иммунность СС-конвейера к 98,6% одиночных ЛС за счет увеличения его аппаратных затрат всего на 1%.

Abstract: The paper estimates the data corruption probability in self-timed circuits manufactured by a standard 65-nanometer and below CMOS process because of short-term soft errors that occurred in the pipeline combinational part. Soft errors appear as a result of the external causes and internal noise sources. The paper analyzes events able to lead to data corruption in the pipeline due to soft errors. In the worth case, self-timed pipeline is naturally immune to 84.4% soft errors in its combinational part due to self-timed circuit features. Proposed layout synthesis techniques increase soft error tolerance of the pipeline up to 85.6%. Indication of the state of the paraphase signal, inversed to its spacer, as spacer provides self-timed pipeline immunity to 98.6% of single soft errors at the expanse of pipeline hardware complexity by less than 1 %.

Устойчивость самосинхронных комбинационных схем к кратковременным логическим сбоям

Степченков Ю. А., Дьяченко Ю. Г., Рождественский Ю. В., Морозов Н. В., Степченков Д. Ю., Дьяченко Д. Ю. Устойчивость самосинхронных комбинационных схем к кратковременным логическим сбоям // Системы и средства информатики, 2020. Т. 30. № 2. С. 4-10.

DOI:10.14357/08696527200201. Индексируется в РИНЦ, ВАК, RSCI.

Аннотация: Рассматривается вопрос устойчивости самосинхронных (СС) комбинационных схем, изготовленных по технологии комплементарный металл — диэлектрик — полупроводник (КМДП), к кратковременным логическим сбоям (ЛС), вызываемым внешними причинами или внутренними помехами, не приводящими к разрушению полупроводниковых структур. Обсуждаются последствия воздействия физических причин, приводящих к ЛС в микросхеме, изготовленной по КМДП-технологии с проектными нормами 65 нм и ниже. Введена классификация ЛС в СС комбинационных КМДП-схемах в зависимости от времени их появления и типа сбоя. Самосинхронные схемы имеют более высокую степень устойчивости к кратковременным ЛС, чем их синхронные аналоги, благодаря двухфазной дисциплине работы, запрос- ответному взаимодействию и парафазному кодированию информационных сигналов. Предложены схемотехнические и топологические методы, обеспечивающие снижение чувствительности СС комбинационных КМДП-схем к логическим сбоям за счет гарантированного отсутствия биполярного влияния источника ЛС на элементы, формирующие парафазные сигналы, и на их трассы в топологи схемы.

Abstract: The paper considers self-timed (ST) complementary metal-oxide- semiconductor (CMOS) combinational circuit tolerance to short-term soft errors caused by the external sources or internal noises that do not lead to semiconductor structure destruction. The paper discusses the consequences of physical causes impact, leading to soft errors in a chip manufactured by the 65-nanometer and below CMOS process. It introduces soft error classification in CMOS ST combinational circuits depending on their appearance time and the type of failure. Self-timed circuits have a higher degree of resistance to short-term soft errors than their synchronous counterparts due to the two-phase operation discipline, request-acknowledge interaction, and dual-rail information signal coding. The paper proposes circuitry and layout methods ensuring the lowering of CMOS ST combinational circuit sensitivity to soft errors due to the guaranteed absence of the bipolar influence of the soft error source on the cells forming dual-rail signals and on their wires in the circuit layout.

Универсальный функциональный метод анализа больших самосинхронных схем

Плеханов Л.П., Захаров В.Н. Универсальный функциональный метод анализа больших самосинхронных схем // Системы и средства информатики, 2020. Т. 30. № 2. С. 11-20.

DOI: 10.14357/08696527200202. Индексируется в РИНЦ, ВАК, RSCI.

Аннотация: Одна из главных задач создания самосинхронных (CC) электронных схем- анализ их самосинхронности. Известные событийные методы не обеспечивают полного анализа СС-схем реальной сложности из-за чрезмерного объема вычислений. В рамках функционального подхода предложен универсальный метод, основанный на автоматическом разделении схемы на минимальные СС-ячейки. Метод позволяет радикально уменьшить необходимые вычисления и анализировать самосинхронность схем любого размера.

Abstract: One of the main tasks of creating self-timed circuits is to analyze their self-synchronicity. Known event-based methods do not provide a complete analysis of self-timed circuits of real complexity due to the excessive amount of calculations. Within the framework of the functional approach, a universal method based on the automatic division of the scheme into minimal self-timed cells is proposed. The method allows one to radically reduce the necessary calculations and analyze self-timed circuits of any size.

Improvement of the Natural Self-Timed Circuit Tolerance to Short-Term Soft Errors

Yuri Afanasyevich Stepchenkov, Anton Nikolaevich Kamenskih, Yuri Georgievich Diachenko, Yuri Vladimirovich Rogdestvenski, Denis Yuryevich Diachenko. Improvement of the Natural Self-Timed Circuit Tolerance to Short-Term Soft Errors / Advances in Science, Technology and Engineering Systems Journal Vol. 5, No. 2, 44-56 (2020).

DOI: 10.25046/aj050206

Abstract: The paper discusses the features of the implementation and functioning of digital self-timed circuits. They have a naturally high tolerance to short-term single soft errors caused by various factors, such as nuclear particles, radiation, and others. Combinational self-timed circuits using dual-rail coding of signals are naturally immune to 91% of typical soft errors classified in the paper. The remaining critical soft errors are related to the state of the dual-rail signal, opposite to the spacer and forbidden in traditional dual-rail coding of signals. Paper proposes to consider this state as the second spacer and to indicate it as a spacer to increase the self-timed circuit tolerance to soft errors. Together with an improved indication of the self-timed pipeline, this provides masking of 100% of the considered typical soft errors in combinational self-timed circuits. Due to internal feedback, self-timed latches and flip-flops are less protected from soft errors, as are synchronous memory cells. But thanks to their indication and the input and output signals generation discipline, they are also immune to 89% of typical soft errors. Usage of the self-timed latches and flip-flops with dual-rail coding of information outputs increases the tolerance of self-timed latches and flip-flops to soft errors by 2%. Application of the DICE-like approach to circuitry and layout design of sequential self-timed circuits provide an increase in their tolerance to the single soft errors up to the level of 100%.

Оптимизация индикации многоразрядных самосинхронных схем

Степченков Ю. А., Дьяченко Ю. Г., Рождественский Ю. В., Морозов Н. В., Степченков Д. Ю., Дьяченко Д. Ю. Оптимизация индикации многоразрядных самосинхронных схем // Системы и средства информатики, 2019. Т. 29. № 4. С. 14-27.

DOI: 10.14357/08696527190402. Индексируется в РИНЦ, ВАК, RSCI.

Аннотация: Индикаторная подсхема в самосинхронных (СС) схемах обеспечивает контроль окончания переключения всех элементов в текущую фазу и управление взаимодействием функциональных блоков. С увеличением разрядности СС-схемы растет и вклад индикаторной подсхемы в задержку переключения схемы. В статье рассматриваются вопросы оптимизации индикаторной подсхемы и организации СС-конвейера для обеспечения более высокого быстродействия всей схемы. Для реализации разряда регистров хранения промежуточных данных в ступенях конвейера предлагается использовать вместо обычного СС-К8-трпггера гистерезисный триггер, имеющий меньшую сложность и обеспечивающий хранение как рабочего, так и спей- серного состояния парафазных данных. Дисциплина управления фазами ступеней конвейера с помощью общих индикаторных выходов соседних ступеней конвейера заменяется принципом поразрядной индикации и управления фазами, использующей параллельность вычислений в многоразрядных СС-схемах. Предлагаемые решения обеспечивают существенное повышение быстродействия СС-схем за счет незначительного усложнения индикаторной подсхемы.

Abstract: Indication subcircuit in self-timed (ST) circuits provides both control of the completion of switching all their cells to the current phase and control of their functional blocks interaction. An increase of the ST-circuit capacity leads to rising contribution of the indication subcircuit to the circuit’s transient delay. The paper discusses the optimization of the indication subcircuit and the organization of the ST-pipeline intended for improving performance of the whole circuit. Register bit for storing intermediate data in the pipeline stages is implemented on the basis of hysteretic trigger instead of traditional RS-trigger. Such register bit has less complexity and provides storing both the work and the spacer states of a dual-rail data. Discipline of the pipeline stage phase control by means of total indication outputs of the adjacent pipeline stages is replaced with bit-wise indication and bit-wise control principle, which utilizes the parallelism of the calculations in the multibit ST-circuits. Proposed solutions essentially improve ST-circuits performance due to a slight complication of the indication subcircuit.

Характеризация последовательностных самосинхронных элементов

Степченков Ю. А., Дьяченко Ю. Г., Морозов Н. В., Степченков Д. Ю., Дьяченко Д.Ю. Характеризация последовательностных самосинхронных элементов // Системы и средства информатики, 2019. Т. 29. № 3. С. 104-113.

DOI:10.14357/08696527190309. Индексируется в РИНЦ, ВАК, RSCI.

Аннотация: Специфика функционирования самосинхронных (СС) схем предъявляет особые требования к процедуре их характеризации. Процедура должна учитывать дисциплину формирования информационных и фазовых сигналов на основе задаваемых пользователем атрибутов входов и выходов характеризуемого элемента. Предложена методика уточнения процесса характеризации для последовательностных CC-элементов, основанная на использовании векторов определения статических значений или направлений переключения входов и выходов. Алгоритмизация и реализация предложенного подхода в новой версии системы автоматизированной характеризации интегральных библиотек (САХИБ) повысили ее эффективность и обеспечили достоверную характеризацию всех типов последовательностных элементов из библиотеки СС-элементов для 65-нанометровой КМОП (комплеменарный металл-оксид-полупроводник) технологии. Автоматическое дополнение в процессе характеризации моделей последовательностных элементов конструкциями анализа порядка изменения сигналов на их входах и предупреждения о некорректной последовательности входов облегчает и ускоряет проектирование CC цифровых схем.

Abstract: Functional specificity of the self-timed circuits makes special requirements to their characterization procedure. This procedure should take into account a signal conditioning discipline for information and phase signals on base of user defined attributes of the characterized cell’s inputs and outputs. The paper describes a technique of adjusting characterization process for sequential self-timed cells. It is based on using vectors that set static values and transition direction for all inputs and outputs. Algorithmization and implementation of the suggested approach in new SAHIB characterization system version have increased its efficiency and provided the valid characterization of all sequential cell types in the self-timed cell library for 65-nanometer standard CMOS (complementary metal-oxide-semiconductor) process. Automatic introduction of the Verilog constructions analyzing change order of all cell inputs and notifying their invalid sequence into the sequential cell models during characterization procedure accelerates and mitigates self-timed circuit design.

Синтез самосинхронных комбинационных секций функциональным методом.

Плеханов Л.П. Синтез самосинхронных комбинационных секций функциональным методом // Системы и средства информатики, 2017. Т. 27. № 2. С. 85-97.

DOI: 10.14357/08696527170208. Индексируется в РИНЦ, ВАК, RSCI.

Аннотация: Для разработки самосинхронных (СС) электронных схем, обладающих уникальными свойствами, необходимы специальные методы. Комбинационные схемы могут быть построены из нескольких секций, представляющих собой множество элементов, выполняющих параллельные функциональные преобразования. Известный событийный метод синтеза СС-схем имеет лишь теоретическое значение и непригоден для реального проектирования. В предлагаемом функциональном методе работа секции описывается не событиями (переключениями элементов), а логическими функциями и уравнениями. Метод заключается в составлении и решении логических уравнений. Метод решает задачу синтеза в самом общем виде и позволяет подбирать элементы для реализации из полузаказных или заказных библиотек.

Abstract: Designing of self-timed electronic circuits having unique properties requires special methods. Combinational circuits can consist of several sections representing a variety of elements performing parallel functional transformations. The known event method of self-timed circuit synthesis has theoretical signifi-cance only and is unsuitable for real design. The author proposes a new method, which describes functional sections not by events (switchs of elements) but by logical functions and equations. The method consists in generating and solving logical equations. The method solves the problem in the most general form and allows choosing elements for circuit implementation from semicustom or custom libraries.

Модели отказоустойчивых самосинхронных схем

Степченков Ю. А., Каменских А. Н., Тюрин С. Ф., Рождественский Ю. В. Модели отказоустойчивых самосинхронных схем // Системы и средства информатики, 2016. Т. 26. № 4. С. 19-30.

DOI: 10.14357/08696527160402. Индексируется в РИНЦ, ВАК, RSCI.

Аннотация: Разработка аппаратуры для цифровых вычислительных систем, отличающейся как высокой надежностью, так и энергоэффективностью, является одной из важнейших задач XXI в. Использование самосинхронных (CC) схем позволяет повысить их энергоэффективность. Однако увеличение аппаратных затрат при CC-исполнении обычной, неотказоустойчивой аппаратуры приводит к снижению ее надежности. Cамосинхронное исполнение отказоустойчивой аппаратуры позволяет повысить не только ее надежность, но и улучшить комплексный показатель «энергозатраты-надежность». Дальнейшее развитие методов обеспечения отказоустойчивости CC-схем с учетом их специфики позволит компенсировать их недостатки, такие как сложность проектирования, за счет значительно лучших комплексных показателей эффективности. В статье разрабатываются модели и алгоритмы обнаружения неисправностей для методов обеспечения активной отказоустойчивости, что позволяет повысить достоверность функционирования (ДФ) и коэффициент готовности.

Abstract: The development of both the reliable and the energy-efficient computing systems is one of most important tasks in the XXI century. The usage of self-timed circuits makes it possible to improve energy-efficiency of a computing system. However, the complexity increase in not fault-tolerant self-timed circuits leads to decrease of reliability. The fault-tolerant self-timed implementation of digital devices makes it possible to increase not only reliability but also the complex index «energy-consumption/reliability.» The further development of synthesis methods of fault-tolerant self-timed circuits will allow to compensate the negative effects of self-timed circuit’s development by the positive effect of complex index increasing. The paper describes the models and algorithms of fault detection which are developed to improve validity and reliability of actively fault-tolerant self-timed circuits.

Анализ самосинхронности электронных схем на нижнем уровне иерархии

Плеханов Л.П. Анализ самосинхронности электронных схем на нижнем уровне иерархии // Системы и средства информатики, 2016. Т. 26. № 2. С. 23-42.

DOI: 10.14357/08696527160202. Индексируется в РИНЦ, ВАК, RSCI.

Аннотация: Самосинхронные электронные схемы, обладающие уникальными свойствами, требуют обязательного анализа на свойство самосинхронности. При анализе необходимо вычислить и проверить все рабочие состояния схемы и переходы между ними. Существующие событийные методы оперируют всеми уравнениями схемы одновременно. Для практических схем большого размера анализ этими методами приводит к неприемлемым вычислительным затратам. Предложенный ранее автором функциональный иерархический метод позволяет анализировать схемы по частям «снизу вверх». Уравнения схемы анализируются только на нижнем уровне иерархии, на верхних уровнях используются взаимосвязи фрагментов и параметры, полученные на нижних уровнях. Метод обеспечивает эффективный анализ схем все возрастающих размеров. В данной статье подробно описывается функциональный метод на нижнем уровне иерархии.

Abstract: Self-timed circuits (independent on element’s delay) have the unique properties of a lack of competitions and safe on Out-Stack-At-Fault (OSAF). They require analysis on self-timing. In the traditional approach — analyzing of elements switching, computational complexity is so great that it does not allow analyzing the most practical circuits. The functional hierarchical method, previously proposed by the author, analyzes logic equations only at the lower level, and at the upper levels, it examines only the relationships between blocks. The suggested method makes it possible to analyze circuits of any size effectively. This article describes in detail this method at the lower level of the hierarchy.

Отказоустойчивый самосинхронный последовательно-параллельный порт: варианты реализации

Степченков Ю. А., Каменских А. Н., Тюрин С. Ф., Дьяченко Ю. Г. Отказоустойчивый самосинхронный последовательно-параллельный порт: варианты реализации // Системы и средства информатики, 2016. Т. 26. № 3. С. 48-59.

DOI: 10.14357/08696527160303. Индексируется в РИНЦ, ВАК, RSCI.

Аннотация: Создание элементов и устройств, сочетающих в себе как надежность (отказоустойчивость), так и энергоэффективность, является одним из важнейших направлений развития вычислительной техники. Применение самосинхронных (СС) схем обусловлено их уникальными свойствами — широким диапазоном работоспособности, самопроверяемостью относительно константных консервативных неисправностей (ККН), снижением энергопотребления. Наличие встроенных элементов рабочего контроля в СС-схемах сделало наиболее перспективными и активно развивающимися методы обеспечения активной отказоустойчивости. Однако для некоторых областей применения необходимо обеспечение пассивной отказоустойчивости. Рассматриваются ключевые отличия в методах обеспечения отказоустойчивости, предлагаются технические решения, реализующие наиболее эффективные методы, и проводится расчет их показателей надежности, а также сравнение с применением комплексных показателей эффективности.

Abstract: The design of digital devices with both reliability and energy-efficiency is one of the important directions of information technologies development. The self-timed circuits have unique properties — width operation range, self-testing for stuck-at faults and energy-consumption decrease. The ability of self-test makes self-repair techniques better and more perspective for self-timed circuits. However, the fault-tolerance is necessary for some fields of application. The key difference between different techniques of reliability improvement is researched in this paper by the example of proposed technical solutions that realize most efficient designing methods. The usage of complex indices provides comparison of designs.

Проблема анализа полумодулярности и энергонадежности отказоустойчивых самосинхронных схем

Каменских А.Н., Степченков Ю.А, Тюрин С.Ф. Проблема анализа полумодулярности и энергонадежности отказоустойчивых самосинхронных схем. // М.: Знак, Электротехника, № 11, 2015. С. 27-31.(индексируется в Scopus).

Kamensky A.N., Stepchenkov Yu.A, Tyurin S.F. Problems of the analysis of semi modularity and power-reliability of fault-tolerant self-timed circuits /M: Electro engineering, 2015, No. 11. p. 27-31 (is indexed in Scopus).

Аннотация: Самосинхронные устройства, не зависящие от задержек элементов часто позиционируют как высоконадежные, однако вопросы создания отказоустойчивых самосинхронных цифровых схем до сих пор изучались слабо. Начав работать в этом направление, авторы адаптировали существующие методы проектирования отказоустойчивых комбинационных схем под самосинхронную реализацию, а также предложили ряд технических решений и методик, позволяющих существенно увеличить надежность узловых элементов – индикаторов окончания переходных процессов. Анализ полученных результатов позволил сделать вывод, что традиционные методы повышения надежности для самосинхронных устройств не позволяют достичь тех параметров, на которые рассчитывают разработчики цифровых устройств. Поэтому одной из ключевых задач на пути к созданию отказоустойчивых самосинхронных схем является разработка оригинальных методов повышения надежности и отказоустойчивого проектирования. При решении этой задачи возникает проблема анализа разрабатываемых отказоустойчивых решений на самосинхронность. В рамках решаемой задачи был сделан переход к вопросам резервирования регистровых структур. В статье анализируется взаимосвязь между масштабированием энергопотребления и надежности. Предлагается показатель энергонадёжности, позволяющий сравнивать цифровые схемы по трем ключевым на взгляд авторов показателям – энергопотребление, надежность, производительность.

Умножитель с накоплением: методологические аспекты

Соколов И.А., Степченков Ю.А., Бобков С.Г., Рождественский Ю.В., Дьяченко Ю.Г. Умножитель с накоплением: методологические аспекты // Системы и средства информатики – М.: т. 24, № 3, 2014 – С. 44-62.

DOI:10.14357/08696527140304

Аннотация: Представлены подходы к проектированию самосинхронной (СС) аппаратуры и рассмотрены условия внутрисистемной интеграции синхронных и СС-устройств в рамках супер-ЭВМ на примере разработки СС-устройства ум-ножения-сложения, соответствующего стандарту IEEE 754 и выполняющего либо одну операцию двойной точности, либо одновременно две операции одинарной точности над тремя операндами. Устройство реализовано по КМОП-технологии с проектными нормами 65 нм с использованием в умножителе самосинхронного троичного кодирования. В зависимости от исполнения оно работает с асинхронным или синхронным окружением и обеспечивает производительность на уровне не менее 1 гигафлопс при времени задержки формирования результата относительно поступления входных операндов не более 6 нс.

Базис реализации супер-ЭВМ эксафлопсного класса

Соколов И.А., Степченков Ю.А., Бобков С.Г., Захаров В.Н., .Дьяченко Ю.Г., Рождественский Ю.В., Сурков А.В. Базис реализации супер-ЭВМ эксафлопсного класса // Информатика и ее применения – М.: ТОРУС ПРЕСС, т. 8, вып. 1, 2014 – С. 45-70.

DOI:10.14357/19922264140106

Аннотация: Статья посвящена выбору схемотехнического базиса реализации микропроцессоров и коммуникационных сред супер-эвм эксафлопсного класса. Проведен сравнительный анализ характеристик цифровых устройств различной сложности, реализованных в синхронном (С) и самосинхронном (СС, self-timed) базисе. Подтверждены основные преимущества СС-схем по сравнению с синхронными аналогами: отсутствие гонок, максимально возможный диапазон работоспособности, высокое быстродействие, относительно низкая мощность потребления. В результате перехода от синхронной к квазисамосинхронной и самосинхронной реализации зона работоспособности устройства расширяется независимо от его сложности. В наибольшей степени эти преимущества проявляются при использовании СС-схем для проектирования надежной цифровой аппаратуры. Рассмотрены различные методологии проектирования СС-схем. Проведен сравнительный анализ реализации СС-схем в обобщенном базисе схем, нечувствительных к задержкам, развиваемом авторами, и в базисе NCL (NULL Convention Logic) схем. Показано, что предлагаемый базис обеспечивает получение схем с лучшими параметрами по быстродействию, аппаратурным затратам и энергопотреблению при проектировании типовых цифровых устройств, составляющих основу для построения современных вычислительных систем и комплексов.

Самосинхронный умножитель с накоплением: практическая реализация

Степченков Ю.А., Дьяченко Ю.Г., Рождественский Ю.В., Морозов Н.В., Степченков Д.Ю., Рождественскене А.В., Сурков А.В. Самосинхронный умножитель с накоплением: практическая реализация // Системы и средства информатики – М.: Т. 24, № 3, 2014. – С. 63-77.

DOI:10.14357/08696527140305

Аннотация: Статья посвящена результатам разработки вариантов независимого от задержек устройства умножения-сложения (SIFMA — Speed-Independed Fused Multiply-Add), соответствующего стандарту IEEE 754 и выполняющего либо одну операцию умножения с накоплением двойной точности, либо одну или две операции одинарной точности над тремя операндами. Устройство разработано по стандартной технологии КМОП (комплементарная структура металл–оксид–полупроводник) с проектными нормами 65 нм. Оно работает с синхронным или асинхронным окружением и обеспечивает среднюю производительность на уровне 1 Гфлопса при напряжении питания 1 В и температуре 25?C. Энергопотребление при этом не превышает 970 мдж/ггц.

Проектирование самосинхронных схем: Структурные методы в иерархическом анализе

Плеханов Л.П. Проектирование самосинхронных схем: структурные методы в иерархическом анализе // Информатика и ее применения. М.: ТОРУС ПРЕСС, 2014 ‑ т. 8, вып. 3. – С. 105-113.

DOI:10.14375/19922264140312

Аннотация: Самосинхронные схемы (СС-схемы) имеют уникальные свойства независимости от задержек И отказобезопасности. Рассмотрена одна из главных проблем проектирования таких схем—анализ самосинхронности больших схем. В традиционном подходе схемы анализируются событийными методами, по переключениям элементов. Сложность вычислений в таком подходе экспоненциально растет от раз- Мера и/или других параметров схем, что не позволяет анализировать большинство практически значимых схем. Решение проблемы предлагается в функциональном подходе—без использования переключений—и иерархическом описании схем. В иерархическом анализе самосинхронности наряду с анализом логиче- Ских функций предлагается использовать структурные методы — исследование взаимосвязей элементов и фрагментов. Такой способ позволяет резко уменьшить трудоемкость вычислений и в итоге решить Одну из главных проблем проектирования СС-схем — анализ схем любого размера. Эффективность предложенных методов подтверждена с помощью экспериментальных программных средств.

Иерархический метод анализа самосинхронных электронных схем

Л. П. Плеханов. Иерархический метод анализа самосинхронных электронных схем // Системы и средства информатики, – М.: ТОРУС ПРЕСС, Т. 22, № 1, 2012 – С. 62-73

Аннотация: Развитию и внедрению самосинхронных схем (СС), обладающих уникальными свойствами, во многом препятствуют трудности проектирования, в частности анализ на самосинхронность «больших» схем. Предлагается иерархический метод анализа схем неограниченного размера, основанный на функциональном подходе. В литературе подобного подхода и метода не отмечено.

Система характеризации самосинхронных элементов

Ю. Г. Дьяченко, Н. В. Морозов, Д. Ю. Степченков, Ю. А. Степченков. Система характеризации самосинхронных элементов // Системы и средства информатики, – М.: ТОРУС ПРЕСС, Т. 22, № 1, 2012 – С. 38-48

Аннотация: Представлена методика характеризации (извлечения временных и электрических параметров для формирования функционально-логической модели) элементов библиотеки для проектирования самосинхронных (СС) схем. Показано, что специфика поведения СС-элементов накладывает дополнительные ограничения на процесс характеризации и приводит к изменению смысла некоторых параметров модели элемента. Описана программная система характеризации СС-элементов. Представлены результаты ее опытной эксплуатации.

Самосинхронные схемы – будущее микроэлектроники

Степченков Ю.А., Дьяченко Ю.Г., Горелкин Ю.А. Самосинхронные схемы – будущее микроэлектроники – «Вопросы радиоэлектроники», серия «Электронная вычислительная техника», выпуск 2 – М.: 2011 – С. 153-184.

Аннотация — Статья посвящена проектированию самосинхронных (СС) схем. На примере СС-устройств различной сложности подтверждаются их основные преимущества по сравнению с синхронными аналогами: отсутствие гонок, максимально возможный диапазон работоспособности, высокое быстродействие, относительно низкая мощность потребления. В наибольшей степени эти преимущества проявляются при использовании СС-схем для проектирования надежной цифровой аппаратуры. В настоящей статье приводятся результаты сравнительных испытаний тестовых кристаллов и моделирования вариантов реализации традиционных и отказоустойчивых синхронных и СС-устройств. Они демонстрируют, что, независимо от сложности устройства, зона его работоспособности расширяется при переходе от синхронной к СС-реализации.

Особенности классификационного анализа самосинхронных схем

Ю. В. Рождественский, Н. В. Морозов, А. В. Рождественске. Особенности классификационного анализа самосинхронных схем // Системы и средства информатики, – М.: ТОРУС ПРЕСС, Т. 21, № 1, 2011 – С. 92-104

Аннотация: Предметом статьи является исследование методов анализа асинхронных схем на независимость их поведения от задержек логических элементов. Предлагаемый метод в теоретической части базируется на диаграммах переходов (метод в глобальных моделях) с последующим тождественным преобразованием к событийным моделям. Полученные алгоритмы анализа обладают строгой фундаментальностью метода в глобальных моделях, но не требует полного перебора достижимых состояний схемы. Сложность задачи изменилась с экспоненциальной на полиномиальную. Классификационный анализ уточняет свойства исследуемой схемы, представляет развернутую диагностику и определяет возможные причины возникших нарушений.

О свойстве самосинхронности цифровых электронных схем

Л.П. Плеханов. О свойстве самосинхронности цифровых электронных схем // Системы и средства информатики, – М.: ТОРУС ПРЕСС, Т. 21, № 1, 2011 – С. 84-91

Аннотация: Обсуждаются понятие самосинхронности с практической точки зрения и его связь с классическим определением независимости от задержек. Показано, что одного свойства независимости от задержек недостаточно для самосинхронности. Приводятся практические следствия теоретических положений при разработке самосинхронных (СС) схем. Дается связь самосинхронности с недавно вступившим в действие новым стандартом по надежности.

Анализ на самосинхронность некоторых типов цифровых устройств

Ю. А. Степченков, Ю. Г. Дьяченко, Ю. В. Рождественский, Н. В. Морозов. Анализ на самосинхронность некоторых типов цифровых устройств // Системы и средства информатики, – М.: ТОРУС ПРЕСС, Т. 21, № 1, 2011 – С. 74-83

Аннотация: Представлен подход к проверке цифровой схемы на самосинхронность с использованием программных средств, реализующих событийный метод анализа. Показано, что стопроцентная тестовая полнота анализа на самосинхронность для регистров сдвига и памяти обеспечивается относительно простыми средствами. Предложена методика отладки схемы в процессе анализа на самосинхронность произвольной схемы. Обоснована необходимость иерархического подхода к анализу сложной схемы на самосинхронность.

Полнота анализа электронных схем на самосинхронность

Плеханов Л.П. Полнота анализа электронных схем на самосинхронность // «Системы и средства информатики» – М.: ТОРУС ПРЕСС, Т. 20, № 1, 2010 – С. 48-58

Аннотация: В статье обсуждаются вопросы полноты анализа самосинхронности схем, связанные с начальными состояниями и изменениями информационных входов. Показано, что неполный учет этих изменений приводит к ошибочным выводам. Получены достаточные для полноты условия изменения информационных входов. Предложены некоторые способы организации полного анализа для событийных методов и функционального метода.

Разработка вычислителя, не зависящего от задержек элементов

Ю. А. Степченков, Ю. Г. Дьяченко, Ю. В. Рождественский, Н.В. Морозов, Д.Ю. Степченков. Разработка вычислителя, не зависящего от задержек элементов // Системы и средства информатики, – М.: ТОРУС ПРЕСС, Т.20, № 1, 2010 – С. 5-23

Аннотация: Представлены результаты практической разработки не зависящего от задержек элементов вычислительного блока (в дальнейшем—вычислителя), выполняющего функции деления и извлечения квадратного корня в соответствии со стандартом IEEE 754. Оптимизированная индикаторная подсхема гарантирует стопроцентный контроль окончания переключений всех элементов схемы вычислителя на каждой фазе работы. Достоверность независимости от задержек элементов обеспечивается иерархическим анализом.

Базисная платформа проекта «Отказоустойчивые вычислительные системы»

Филин А.В. Базисная платформа проекта «Отказоустойчивые вычислительные системы» // Системы и средства информатики, – М.: ТОРУС ПРЕСС, Т. 19, 2009 – С. 149-177

Аннотация: В статье повествуется о системообразующей платформе проекта создания архитектуры и опытного образца отказоустойчивой ВС (ОВС), разрабатывавшейся в 80-х годах прошлого столетия и предназначавшейся для построения компьютерных систем управления после 2000-го года. Это обстоятельство требовало прогноза развития техники надёжных вычислений на 10 лет вперёд и устанавливало, тем самым, будущие характеристики ОВС на уровне вычислительных систем следующего (четвёртого) поколения. Когда страна, наконец, повернулась лицом к этой проблеме, мировое компьютеростроение было на подъёме и успешно осваивало производство ОВС третьего поколения. Общие сведения о содержании проекта «ОВС», прерванного по объективным причинам в 80-е годы прошлого столетия, описаны в [1].

Реализация функционального метода анализа самосинхронности электронных схем

Плеханов Л.П. Реализация функционального метода анализа самосинхронности электронных схем // Системы и средства информатики, – М.: ТОРУС ПРЕСС, Т. 19, 2009 – С. 142-148

Аннотация: В статье описываются вопросы расширенной реализации впервые разработанного функционального метода анализа самосинхронности электронных схем. Использование свойства индицируемости сигналов в данном методе позволяет определить независимость работы схемы от задержек её элементов (самосинхронность), а также получить необходимую информацию об индицируемости внешних и внутренних сигналов схемы. В расширенной реализации, помимо собственно анализа самосинхронности, производится вычисление параметров, необходимых и достаточных для применения схемы, без её раскрытия, в самосинхронных схемах более высокого уровня. Расширенные задачи реализованы в программе анализа ФАЗАН, которая, как и предыдущая реализация, характеризуется полиномиальной сложностью вычислений от числа элементов.

Квазисамосинхронная реализация устройства деления и извлечения квадратного корня

Степченков Ю.А., Дьяченко Ю.Г., Рождественский Ю.В., Морозов Н.В., Степченков Д.Ю. Квазисамосинхронная реализация устройства деления и извлечения квадратного корня // Системы и средства информатики, М.: Наука, вып. 18, 2008. – С. 234-260.

Аннотация: Представлены подходы к проектированию самосинхронной аппаратуры различных классов; рассмотрены условия интеграции синхронных и самосинхронных устройств на примере разработки квазисамосинхронного вычислительного устройства, выполняющего функции деления и извлечения квадратного корня над числами одинарной и двойной точности в соответствии со стандартом IEEE 754.

Анализ самосинхронности электронных схем функциональным методом

Плеханов Л.В. Анализ самосинхронности электронных схем функциональным методом // Системы и средства информатики, М.: Наука, вып. 18, 2008. – С. 225-233

Аннотация: В статье описывается впервые разработанный функциональный метод анализа самосинхронности электронных схем на основе индицируемости сигналов. В отличие от событийных функциональный метод позволяет получить детальную информацию об индицируемости внутренних и внешних сигналов схемы за один сеанс, сразу по всем сочетаниям параметров схемы. Метод позволяет исследовать более широкий, чем ранее, класс неисправностей, а также открывает путь для анализа схем практически неограниченного размера. Метод характеризуется полиномиальной сложностью вычислений от числа сигналов схемы. На основе функционального метода создана программа анализа самосинхронности САМАН.

Суперкомпьютинг и классические компьютеры

Филин А.В. Суперкомпьютинг и классические компьютеры // Системы и средства информатики, М.: Наука, вып. 17, 2007. – С. 468-491.

Аннотация: В работе продолжен анализ состояния отрасли сверхбыстрых вычислений, начатых в [1]. Показано, что ведущие изготовители СБИС-микропроцессоров общего назначения (корпорации Intel, AMD, IBM и д р.) Приступили к реализации многоядерной концепции их построения. Этим событием они обозначили, что дальнейшее повышение производительности однопроцессорных компьютеров исчерпало себя экономически И пришло время компьютеров на основе многоядерных процессоров. В качестве одной из основных областей применения многоядерных процессоров рассматривается сектор суперкомпьютеров и суперкомпьютинга. Никаких других альтернативных предложений тому, что реализуют ведущие микропроцессорные корпорации, не обнаружено.

Самосинхронные последовательностные схемы: опыт разработки и рекомендации по проектированию

Степченков Ю.А., Дьяченко Ю.Г., Петрухин В.С. Самосинхронные последовательностные схемы: опыт разработки и рекомендации по проектированию // Системы и средства информатики, М.: Наука, вып. 17, 2007. – С. 503-529.

Аннотация: Самосинхронные (СС) схемы из области теоретических исследований активно переходят в область практических разработок, находя применение в широкой номенклатуре вычислительных устройств (ВУ). Этому способствуют такие свойства СС-схем, как независимость работоспособности от задержек составляющих элементов, естественная надежность, работоспособность в значительно более широком диапазоне изменяющихся параметров окружающей среды и напряжения питания. В данной работе представлены рекомендации по проектирования последовательностных СС-схем, выполненных по КМОП технологии (комплементарный металл-оксид-полупроводник). Приводится сравнительный анализ характеристик последовательностных синхронных и СС-схем, полученных с помощью моделирования и натурных испытаний образцов. Результаты испытаний показывают, что использование СС-схемотехники обеспечивает улучшение характеристик при реализации последовательностных схем, особенно для их отказоустойчивых вариантов.

Суперкомпьютеры и суперкомпьютинг: состояние проблемы параллельных вычислений

Филин А.В. Суперкомпьютеры и суперкомпьютинг: состояние проблемы параллельных вычислений // Системы и средства информатики, М.: Наука, вып. 17, 2007. – С. 391-467.

Аннотация: Описаны результаты достижений интернациональной отрасли сверхбыстрых вычислений (суперкомпьютинга) по состоянию на июль 2006 года. Показано, что в жёсткой конкуренции суперкомпьютерных архитектур победу одерживает класс суперкомпьютеров кластерного типа на основе неймановской концепции параллелизма, известной как «модель клеточных автоматов». Рассмотрены намерения и перспективные планы изготовителей суперкомпьютерных систем в США, Японии, Великобритании, Китае и других странах. Сформулированы обобщающие выводы, характеризующие текущее состояние и перспективы отрасли сверхбыстрых вычислений.

Самосинхронность и задачи анализа строго самосинхронных электронных схем

Плеханов Л.П. Самосинхронность и задачи анализа строго самосинхронных электронных схем // Системы и средства информатики, М.: Наука, вып. 17, 2007. – С. 492-502.

Аннотация: Дано обоснование возможности применения чисто функционального понятия самосинхронности на основе индицируемости, не связанное с событийными моделями, для анализа больших ССС-схем. Приведены соответствующие постановки задач анализа, отличные от используемых в настоящее время.

Самосинхронные схемы – ключ к построению эффективной и надежной аппаратуры долговременного действия

Ю.А. Степченков, Ю.Г. Дьяченко, В.С. Петрухин, Л.П. Плеханов. Самосинхронные схемы – ключ к построению эффективной и надежной аппаратуры долговременного действия // Наукоемкие технологии. № 5-6, 2007, т. 8, с. 73-88.

Аннотация: Самосинхронные (СС) схемы завоевывают все большую популярность в среде разработчиков цифровой аппаратуры. В последнее время эти схемы в том или ином виде (строго самосинхронные или квазисамосинхронные) все чаще используются в коммерческих изделиях. Основные их преимущества заключаются в отсутствии гонок, максимально возможном диапазоне работоспособности, высоком быстродействии и относительно низкой мощности потребления. Одним из наиболее важных потенциальных преимуществ СС-схем является их естественная приспособленность к проектированию надежной цифровой аппаратуры. В настоящей статье приводятся результаты разработки, сравнительных испытаний тестовых образцов и моделирования вариантов реализации отказоустойчивых устройств на базе синхронного и самосинхронного подходов. Результаты испытаний показывают, что принадлежность аппаратуры к классу СС-схем позволяет получить наиболее эффективные решения для отказоустойчивых устройств.

Самосинхронная схемотехника ─ перспективный путь реализации аппаратуры

И.А.Соколов, Ю.А.Степченков, В.С.Петрухин, Ю.Г.Дьяченко, В.Н.Захаров. Самосинхронная схемотехника – перспективный путь реализации аппаратуры // Системы высокой доступности. № 5-6, 2007, т. 8, с. 61-72.

Аннотация: Методология проектирования самосинхронной (СС) цифровой аппаратуры была областью активных теоретических исследований с середины 1950-ых годов, и в последнее время ее элементы все чаще используются в коммерческих изделиях. В настоящей статье приводятся результаты разработки и сравнительных испытаний тестовых образцов двух вариантов реализации ядра микроконтроллера: традиционного (синхронного) и строго самосинхронного (ССС). Результаты испытаний показывают, что принадлежность аппаратуры к классу ССС-схем позволяет наиболее полно реализовать возможности СС-схемотехники: максимальный диапазон работоспособности, высокое быстродействие и относительно низкую мощность потребления.

Универсальная подсистема анализа самосинхронных схем

Рождественский Ю.В., Морозов Н.В., Степченков Ю.А., Рождественскене А.В. Универсальная подсистема анализа самосинхронных схем // Системы и средства информатики, М.: Наука, вып. 16, 2006. – С. 463-475.

Аннотация: Рассматривается анализ асинхронных схем на независимость их поведения от задержек элементов. Такие схемы называются самосинхронными. Анализ основан на построении диаграмм переходов, покрывающих все возможные состояния схемы, и относится к методам анализа схемы в глобальных состояниях. Главное преимущество этих методов заключается в их универсальности – возможности применения для анализа всех классов самосинхронных схем. Рассматриваемая подсистема АСИАН представляет собой комплекс программ, позволивший многократно сократить временные затраты на процедуру анализа по сравнению c существующими аналогами и, по существу, реализовать максимально возможную эффективность анализа.

Экспериментальная проверка некоторых свойств строго самосинхронных схем

Плеханов Л.П., Степченков Ю.А. Экспериментальная проверка некоторых свойств строго самосинхронных схем // Системы и средства информатики, М.: Наука, вып. 16, 2006. – С. 476-485.

Аннотация: Впервые в России в рамках полузаказной БМК-технологии (БМК – базовые матричные кристаллы) проведено прямое экспериментальное исследование ряда теоретически утверждаемых свойств строго самосинхронных (ССС) схем: независимости работы от задержек элеметов, широкой области эксплуатации и безопасности функционирования. Приводятся результаты исследования двух реализаций сравнительно простой экспериментальной ССС-микросхемы в широком диапазоне питающих напряжений и температур. Проведенные эксперименты подтверждают теоретические выводы по поведению ССС-схем и, в первую очередь, беспрецедентно широкий диапазон их работоспособности.

Система тестирования самосинхронных микросхем

Петрухин В.С., Степченков Ю.А., Морозов Н.В., Степченков Д.Ю. Система тестирования самосинхронных микросхем // Системы и средства информатики, М.: Наука, вып. 16, 2006. – С. 486-495.

Аннотация: Рассмотрены основные проблемы сопряжения контрольно- измерительного оборудования с самосинхронными микросхема ми. Для проведения тестирования и сравнительных испытаний синхронного и самосинхронного образцов микросхем в лабораторных условиях рассмотрена структура аппаратных и программных средств системы автоматизированного тестирования опытных кристаллов (САТОК). Детально представлен интерфейс взаимодействия пользователя с системой тестирования.

Проблемы функционального подхода в проектировании самосинхронных схем

Плеханов Л.П. Проблемы функционального подхода в проектировании самосинхронных схем // Системы и средства информатики, М.: Наука, вып. 15, 2005. – С. 329-337.

Аннотация: В статье рассматриваются схемы, относящиеся к полумодулярным по Маллеру – строго самосинхронные схемы (ССС-схемы). Традиционно сложилось так, что методы проектирования ССС-схем основываются на представлении в виде изменений значений переменных схемы – событий. В работах Д.Маллера [1] и других использовались диаграммы переходов (ДП) – изменения полных состояний, то есть наборов значений всех переменных. В.И.Варшавский с сотрудниками применили более компактное представление – диаграммы изменений (ДИ) [2], где указывается только та переменная, которая изменяется в текущем событии. Развиваются также и представления в виде сетей Петри. Такой подход далее будем называть событийным.

Библиотека элементов базовых матричных кристаллов для критических областей применения

Степченков Ю.А., Денисов А.Н., Дьяченко Ю.Г., Гринфельд Ф.И., Филимоненко О.П., Фомин Ю.П. Библиотека элементов базовых матричных кристаллов для критических областей применения // Системы и средства информатики, М.: Наука, вып. 14, 2004. – С. 318-361.

Аннотация: В последнее время возобновился интерес зарубежных специалистов к самосинхронным системам из-за их устойчивости к ошибкам, малой мощности потребления и хорошей производительности [1, 2]. Для российской электронной техники это особенно актуально. Многие из современных систем управления вооружением, стоящим на боевом дежурстве в России, близки к выработке своего морального и физического ресурсов.

Синтез комбинационных самосинхронных электронных схем

Плеханов Л.П. Синтез комбинационных самосинхронных электронных схем // Системы и средства информатики, М.: Наука, вып. 14, 2004. – С. 292-304.

Аннотация: В статье рассматриваются строго самосинхронные (ССС) схемы КМДП-технологии. Эти схемы будут представляться в парафазном (ПФ) коде, так как иные представления приводят к чрезмерной сложности и не имеют практического значения.

Индикация в самосинхронных электронных схемах. Обоснование и оптимизация

Плеханов Л.П. Индикация в самосинхронных электронных схемах. Обоснование и оптимизация // Системы и средства информатики, М.: Наука, вып. 12, 2002. – С. 290-297.

Аннотация: Индикация в строго самосинхронных электронных схемах (ССС-схемах) является главным отличием таких схем от обычных синхронных, и именно она обеспечивает уникальные свойства самосинхронных схем Под индикацией в ССС-схемах будем понимать такое их построение, которое обеспечивает установление выходных сигналов в очередную временную фазу (рабочую или промежуточную — спейсер) тогда и только тогда, когда на входах установятся сигналы той же фазы

Базовые элементы самосинхронных схем кмдп технологии

Плеханов Л.П. Базовые элементы самосинхронных схем КМДП-технологии // Системы и средства информатики: Вып. 11 – М.: Наука, 2001. – С. 316-320.

Аннотация: В исследовании и развитии самосинхронной схемотехники, принятой в качестве схемотехнической основы СБИС естественно-надёжных компьютеров, одной из базовых технологий рассматривается КМДП (КМОП) технология. Эта технология в настоящее время позволяет достигать наибольшей степени интеграции схем. В связи с этим необходимо отчётливо представлять, на каких базовых элементах КМДП технологии можно реализовывать самосинхронные схемы.

Направления развития интегральной элементной базы для компьютеров следующего поколения

Филин А.В. Направления развития интегральной элементной базы для компьютеров следующего поколения // Системы и средства информатики: Вып. 10 – М.: Наука, 2000. – С. 277-289.

Аннотация: Среди множества проблем проектирования компьютеров новых поколений (КНП) проблема создания элементной базы (ЭБ) для них является наиболее важной, поскольку именно она определяет границы между поколениями этого вида средств вычислительной техники. По крайней мере, так было при смене первых четырех состоявшихся поколений компьютеров.

Самосинхронная схемотехника – альтернатива синхронной

Степченков Ю.А., Дьяченко Ю.Г., Петрухин В.С., Филин А.В. Самосинхронная схемотехника – альтернатива синхронной // В сб. «Научные труды ОИВТА РАН», 1999, 10 с.

Аннотация: В работе подводятся итоги сравнительного проектирования представительных тестовых устройств (регистрового и комбинационного типов) в синхронном (С) и строго самосинхронном (СС) базисах. Показано, что применение СС-схемотехники в отказобезопасных и отказоустойчивых устройствах (и системах) наиболее предпочтительно, т.к. обеспечивает более высокое быстродействие при меньших аппаратных затратах и энергопотреблении по сравнению с их С-аналогами.

Компьютеры без синхронизации

Филин А.В., Степченков Ю.А. Компьютеры без синхронизации // Системы и средства информатики: Вып. 9 – М.: Наука, Физматлит, 1999. – С. 242-246.

Аннотация: С момента появления компьютеров их производительность повышается, в основном, за счет усложнения структуры устройств (повышения степени параллелизма) и увеличения степени интеграции и тактовой частоты элементной базы. В последние годы частота синхронизации стала для компьютеров «числом Маха» — той единственной характеристикой, которая позволяет различать компьютеры, идентичные по всем другим показателям. Ввиду этой символической значимости частоты синхронизации кажется невозможным представить себе компьютер без традиционной (принудительной) синхронизации.

Цена реализации уникальных свойств самосинхронных схем

Степченков Ю.А., Дьяченко Ю.Г., Петрухин В.С., Филин А.В. Цена реализации уникальных свойств самосинхронных схем // Системы и средства информатики, М.: Наука, вып. 9, 1999. – С. 261-292.

Аннотация: Для подтверждения объявленных уникальных свойств строго самосинхронных (ССС) схем и определения «цены» их реализации (на количественном уровне) в сравнении с синхронными (С) схемами были тщательно разработаны альтернативные варианты ССС- и С-схем специально выбранных тестовых функциональных устройств (ТФУ) и проведены их модельные испытания на компьютере. ТФУ должны были удовлетворять целому ряду требований и, в первую очередь, быть функционально законченными, расширяемыми по разрядности и достаточно простыми в реализации, чтобы можно было рассмотреть разные варианты их исполнения: традиционный (несамопроверяющийся, то есть безызбыточный), самопроверяющийся и отказоустойчивый.

Автоматизация разработки электронных строго самосинхронных кмдп-схем

Плеханов Л.П. Автоматизация разработки электронных строго самосинхронных кмдп-схем // Системы и средства информатики, М.: Наука, вып. 9, 1999. – С. 292-300.

Аннотация: Несмотря на значительное развитие теории самосинхронных (СС) и родственных им схем, их практическая реализация является делом весьма трудным и новым. Это связано с тем, что существующие теории и созданные на их основе инструментальные средства не учитывают многие “земные” проблемы конкретной схемотехники — такие, как согласование нагрузок, ограничения на реализуемые функции со стороны технологии, экономию площади кристалла и другие. Существующая не совсем четкая терминология в области несинхронных схем и неоднозначное использование термина “самосинхронность” приводят к необходимости более точного обозначения рассматриваемого класса схем, которые ранее назывались самосинхронными. Строго самосинхронной схемой (ССС-схемой) будем называть такую разомкнутую схему, которая при корректном замыкании образует полумодулярную (по Маллеру) схему.

Самосинхронизация — естественный путь обеспечения долгоживучести интегральных схем

Филин А.В. Самосинхронизация — естественный путь обеспечения долгоживучести интегральных схем // Системы и средства информатики: Вып. 9 – М.: Наука, Физматлит, 1999. – С. 242-246.

Аннотация: Всего несколько десятилетий отделяет нас от времени, когда техническое творчество в обществе основывалось на принципах механики. Основным строительным материалом создававшихся технических механизмов и механических систем служили металлические материалы (прежде всего, железо и его сплавы). Теперь же пришло время информатики и информационных компьютерных технологий, когда основой технического творчества являются электронные цифровые компьютеры (далее — компьютеры) в микроэлектронном исполнении. Благодаря постоянным успехам в области технологий производства интегральных схем (ИС) — физической элементной базы цифровых компьютеров — они быстро совершенствуются. Считается, что с момента появления кремниевой интегральной технологии производства элементной базы для компьютеров начала отсчет современная компьютерная техника.