#### 1. Техническое описание.

#### Назначение

МБИС "Контроллер последовательного канала" (далее по тексту МБИС) предназначена для работы в составе троированной бортовой аппаратуры и обеспечивает преобразование параллельного интерфейса в последовательный и обратно.

#### 2 Состав

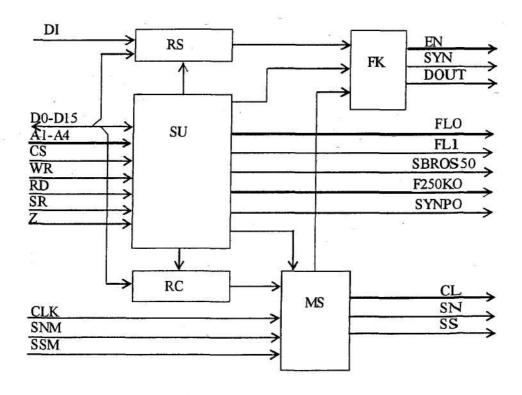

В состав МБИС входят следующие узлы и блоки:

- схема управления SU;

- формирователь последовательного кода FK;

- регистр управления RC;

- сдвиговый регистр RS;

- схема межканальной синхронизации MS.

Структурная схема МБИС показана на рисунке 1.

Рисунок 1 - Структурная схема МБИС

Номера, обозначения и назначение внешних выводов приведено в Таблице 1.

Таблица 1. Внешние выводы МБИС.

| Выводы     |                              | Используе-<br>нам |         | E)      |                               |

|------------|------------------------------|-------------------|---------|---------|-------------------------------|

| микросхемы |                              | COCT              | PERHING | F       |                               |

| Ho-        | Условное<br>обозначе-<br>ние | Вход              | Выход   | D Y 5 K | Назначение                    |

|            |                              |                   |         | a       |                               |

|            | DO                           | 01                | LHZ     | 1       | Вход/выход разряда 0 данимх   |

| 2          | D1                           | 01                | LHZ     |         | Бход/выход равряда 1 данных   |

| 3          | D2                           | 01                | LHZ     | -       | Вкод/выход разряда 2 данных   |

| 4          | D3                           | 01                | LHZ     | -       | Вход/выход разряда 3 данных   |

| 5          | D4                           | 01                | LHZ     | _       | Вкод/выход разряда 4 данных   |

| 6          | D5                           | 01                | LHZ     |         | Вход/виход разряда 5 даниях   |

| 7          | De                           | 01                | LNZ     |         | Вход/выход разряда 6 даниях   |

| á          | 07                           | 01                | LHZ     | -       | Вход/выход разряда 7 даниых   |

| 9          | DB                           | 01                | LHZ     | -       | бход/выход разряда 8 данных   |

| 10         | 09                           | 01                | LHZ     | -       | Вход/выход разряда 9 даювых   |

| 11         | D10                          | 01                | LHZ     | _       | Вход/выход разряда 10 данных  |

| 12         | D11                          | 01                | LHZ     | l _     | Вход/выход разряда 11 данных  |

| 13         | D12                          | 01                | LHZ     | _       | Вход/выход равряда 12 дажих   |

| 14         | D13                          | 01                | LHZ     |         | вход/выход разряда 13 данных  |

| 15         | D14                          | 01                | LHZ     | _       | Вход/выход разряда 14 данных  |

| 16         | D15                          | 01 .              | LHZ     | _       | Вход/выход разряда 15 даниых  |

| 17         | Al                           | 01                |         | _       | Вход разряда 1 адреса         |

| 18         | A2                           | 01                | _       | _       | Вход разряда 2 адреса         |

| 19         | EA                           | 01                | _       |         | Вход равряда 3 вдреся         |

| 20         | A4                           | 01                | _       |         | Еход разряда 4 адреса         |

| 22         | EN                           | -                 | ĹН      | _       | Выход разрешения              |

| 23         | SYN                          |                   | LH      |         | Выход синхронизации дажных    |

| 24         | DOUT                         |                   | LH      | -       | Выход последовательных данных |

| 25         | CL                           | -                 | LH      | ×       | Выход тактовой частоты 4МГц   |

| 26         | FLO                          | **                | LHZ     |         | Выход флага прерывания 0      |

| 27         | FL1                          | _                 | LHZ     | -       | Выход флага прерывания 1      |

| 28         | Z                            | 01                | -       | _       | Технологический вход          |

| 29         | SBROS50                      | -                 | LHZ     | x       | Выход схамы управления        |

| 30         | F250K0                       |                   | LHZ     | x       | Выход частоты 250 КГц схемы   |

|            | 220000                       |                   |         |         | синхроннавции                 |

| 31         | SYNP0                        | -                 | LHZ     | ×       | Выход частоты схемы           |

|            |                              |                   |         |         | синкронивации                 |

| 32         | SS                           |                   | LH      | ×       | Выход синхронизации МЕИС      |

| 33         | SSM                          | 01                | -       | -       | Вход синхронизации МВИС       |

| 34         | SN                           | -                 | LH      | ×       | Выход сигиала начала обмена   |

| 35         | SNM                          | 01                | -       | -       | Вход сигнала начала обмена    |

| 36         | DI                           | 01                |         | -       | Вход последовательных данных  |

| 37         | SP.                          | 01                | *       | -       | Вход начальной установки      |

| 30         | CLK                          | 01                |         | -       | Вход тактовой частоты 12МГц   |

| 39         | RD                           | 01                | -       | -       | Вход сигнала чтения           |

| 40         | WR                           | 01                | -       | **      | Вход сигнала записи           |

| 41         | CS                           | 01                | -       | -       | Вход выборки МБИС             |

Тел.:(+7-499)720-89-92

Факс:(+7-495)913-21-92

# 3. Описание работы

3.1 Работа МБИС по параллельному интерфейсу. Схема управления SU.

Схема управления SU обеспечивает работу МБИС по параллельному интерфейсу Также схема управления предназначена для дешифрации адресов регистров МБИС Совокупность сигналов «CS», «WR», «RD» (активный низкий уровень) и сигналов с дешифратора адресов образует внутренние сигналы записи и чтения для регистров RS и RC. Переключение направления работы выводов D0-D15 осуществляется в SU в зависимости от режима записи или чтения. В SU формируются внутренние сигналы для управления работой формирователя последовательного кода и соответственно работы последовательного интерфейса и сигналы управления для схемы синхронизации.

Флаги прерываний FLO и FL1 вырабатываются в SU в зависимости от состояния бита RDY регистра RC. Наличие "1" в разряде RDY говорит о готовности «подчиненной» МБИС (разрабатываемая МБИС находится в режиме «главный»), при этом выдаются FLO или FL1 при снятой маске активным низким уровнем. Во всех остальных случаях на выходах FLO и FL1 активные высокие уровни сигналов.

Тестовый сигнал F250K0 (частота 250 к $\Gamma$ ц) вырабатывается схемой синхронизации и говорит о том, что схема синхронизации генерирует частоты. Тестовый сигнал SYNP0 вырабатывается в схеме управления и соответствует частоте SYN с учетом разрядов 4х и 2х в регистре RC. Тестовый сигнал SBROS50 вырабатывается схемой управления и служит для сброса бита TR в регистре RC.

В состав параллельного интерфейса входят следующие сигналы, поступающие на схему управления SU:

```

-«D0»-«D15» двунаправленная шина данных(O15-старший разряд);

- «A1»-«A4» разряды адреса-для дешифрации регистров МБИС;

- «CS» сигнал выборки МБИС;

- «WR» сигнал записи в МБИС;

- «RD» сигнал чтения из МБИС;

- «SR» сигнал начальной установки;

- «CLK» тактовая частота 12 МГц;

```

Работа осуществляется в двух форматах - записи и чтения.

Перед началом работы с МБИС необходимо подать сигнал SR начальной установки активным низким уровнем.

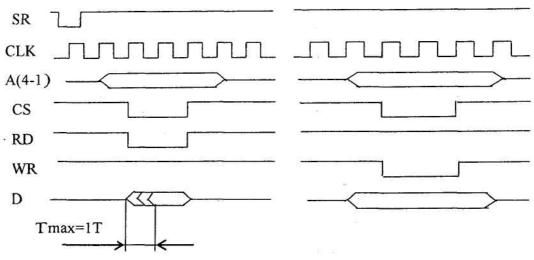

Чтение параллельного кода из сдвигового регистра RS осуществляется после приёма 16-разрядного слова по последовательному интерфейсу (об этом свидетельствует сброшенный бит TR в регистре RC). Для этого нужно установить адрес регистра RS (см. таблицу АЛ), а сигнал выборки микросхемы «СS» и сигнал чтения «RD» установить через такт после установки адреса, активным низким уровнем, длительностью не менее 2-х тактов частоты CLK(В соответствии с временной диаграммой на рисунке A.2). Достоверные данные появляются на шине D не позднее чем через такт частоты CLK. Чтение из регистра RC можно производить в любой нужный момент времени.

Запись параллельного кода в регистр RC осуществляется для конфигурирования режимов работы МБИС. Запись параллельных данных в регистр RS осуществляется для их преобразования в последовательный код и выдачи по последовательному интерфейсу обмена. Для записи нужно установить адрес нужного регистра и данные на такт раньше, чем сигналы выборки микросхемы «CS» и сигнала записи «WR», которые подаются активным низким уровнем, длительностью не менее 2-х тактов частоты CLK(в соответствии с временной диаграммой на рисунке 2).

Тел.:(+7-499)720-89-92

Факс:(+7-495)913-21-92

Рисунок 2 - Временные диаграммы параллельного интерфейса

Адреса регистров МБИС представлены в таблице 1. Таблица 1. - Адреса регистров МБИС

| A4 | A3  | A2 | Al | Разряды адреса | 15    |

|----|-----|----|----|----------------|-------|

| 0  | 0   | 0  | 0  | Регистр RC     | ¥ - 2 |

| 0  | 0 - | 0  | 1  | Регистр RS     | -     |

3.2 Работа МБИС по последовательному интерфейсу. Формирователь последовательного кода.

Обмен последовательным кодом ведется между разрабатываемой МБИС, находящейся в режиме «главный», и одной МБИС, находящейся в режиме «подчиненный». В обмене участвуют следующие сигналы:

«DOUТ» - выход последовательных данных;

«SYN» - выход синхронизации данных;

«EN» - выход разрешения;

«DI» - вход последовательных данных.

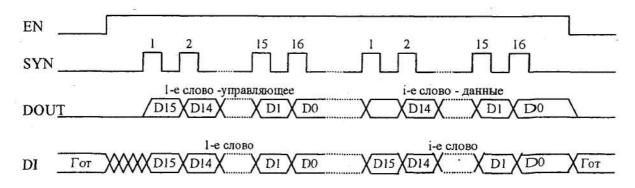

Временная диаграмма обмена последовательным кодом приведена на рисунке 3.

Рисунок 3 - Временная диаграмма обмена последовательным: кодом

Обмен ведется посылками, содержащими одно или несколько 16-ти разрядных слов. Слова, относящиеся к одной посылке, объединены сигналом «EN», имеющим высокий уровень. Низкий уровень сигнала «EN» соответствует паузе между различными посылками.

Одновременно ведется передача данных от «главной» МБИС к «подчиненной» и обратно. При этом, в зависимости от назначения посылки, данные, передаваемые в одном из

направлений, могут не использоваться и не анализироваться, хотя, в принципе, могут одновременно использоваться оба направления передачи данных.

Первое слово в посылке, идущее от «главной» МБИС, является управляющим, в нем содержится управляющая информация, остальные слова служат для передачи данных. Временной интервал между окончанием импульсов синхросигнала «SYN» одной посылки и началом аналогичных импульсов, непосредственно следующих за ними и относящимися к другой посылке, должен быть не менее 2 мкс.

Структура управляющего слова определяется разработчиком «подчиненной» МБИС.

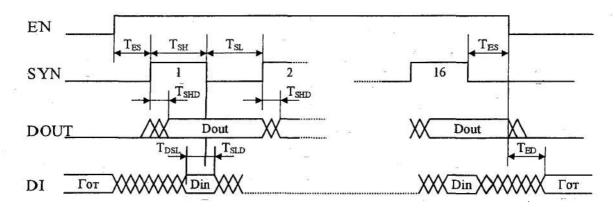

В ответной посылке, идущей от «подчиненной» МБИС к «главной» первое слово содержит содержимое регистра флагов «подчиненной» МБИС, а содержимое последующих слов определяется управляющей информацией. В паузах между посылками, когда сигнал «EN»=0, «подчиненная» МБИС на свой выход выдаёт обобщенный признак готовности, который поступает на вход DI «главной» МБИС и может быть опрошен при чтении регистра 11С.Временные параметры «главной» МБИС представлены на рисунке А.4 и в таблице 2

Рисунок 4 — Временные параметры МБИС Таблица.2

## Временные параметры МБИС

| Параметр                                                                                                                       | Обозн            | Мин.                      | Макс.                        |

|--------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------|------------------------------|

| Интервал между передним фронтом сигнала «EN» и первым тактовым импульсом и между окончанием последнего импульса и снятием «EN» | TES              | 2 x T <sub>CL</sub>       | •                            |

| Длительность тактового импульса                                                                                                | T <sub>SH</sub>  | 1,2,4,8 x T <sub>CL</sub> |                              |

| Пауза между тактовыми импульсами в пределах одного слова                                                                       | T <sub>SL</sub>  | $1,2,4,8 \times T_{CL}$   |                              |

| Время установки выходных данных после переднего фронта<br>синхроимпульса                                                       | T <sub>SHD</sub> | -                         | 50 нс                        |

| Время предустановки входных данных перед задним фронтом<br>синхроимпульса                                                      | $T_{DSL}$        | 100 нс                    | -                            |

| Время удержания входных данных после заднего фронта синхроимпульса                                                             | $T_{SLD}$        | 50 нс                     | =1                           |

| Время установки сигнала достоверного сигнала готовности после<br>снятия сигнала «EN»                                           | $T_{ED}$         | =1                        | 1,2,4,8<br>x T <sub>CL</sub> |

Тел.:(+7-499)720-89-92

Факс:(+7-495)913-21-92

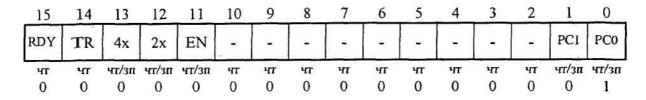

# 3.3 Регистр управления RC

Формат регистра управления RC следующий:

Назначение разрядов регистра RC следующее:

Разряд PC(0) - маска на прерывание, доступен по записи и чтению, исходное состояние "1". При PC(0) = 1 прерывания замаскированы. При PC(0) = 0 маска снята.

Разряд PC(1) - направление прерывания, доступен по записи и чтению, исходное состояние "O". При PC(1) = 0 выдается FLO (26 вывод МБИС). При PC(1) = 1 выдаётся FL1 (27 вывод МБИС).

Разряд RDY представляет собой «защелку», управляемую битом EN регистра RC. При EN=O в нём отображается текущее состояние входа DI. При E№=1 состояние регистра «защелкивается» и не изменяется. Разряд доступен только по чтению. В исходном состоянии бит EN=0, поэтому регистр отображает исходное состояние входа DI.

Разряд TR показывает, что текущая операция выдачи слова из сдвигового регистра RS и приема слова в регистр RS еще не завершена. Разряд доступен только по чтению, аппаратно устанавливается в «лог. 1» при записи в регистр RS и сбрасывается в «лог. О» после окончания выдачи слова из регистра RS и, соответственно, приема слова в регистр RS.

Разряды 12 и 13 определяют длительность сигналов синхронизации SYN и пауз между ними. При нулевом содержимом разрядов 4х и 2х эта длительность равняется одному периоду тактовой частоты СL (4 МГц). Установка в «лог. 1» одного или обоих разрядов приводит к увеличению длительности сигналов «SYN» и пауз между ними в соответствующее число раз. Таким образом, доступна длительность тактовых импульсов в 1, 2, 4 и 8 периодов частоты CL. Разряды 12 и 13 доступны по записи и чтению.

Разряд EN управляет состоянием выхода EN и «защелкой» бита RD У. Разряд может быть программно установлен и сброшен, кроме этого он аппаратно устанавливается в «логическую 1» при выполнении операции записи в сдвиговый регистр RS.

Разряды 2-10 не используются, доступа по записи нет, при чтении должны выдавать нулевой код.

## 3.4 Сдвиговый регистр RS

Выходной сдвиговый регистр RS предназначен для преобразования записанных в него в параллельном коде 16-разрядных данных в последовательный код и для преобразования поступающего на его вход последовательного кода в 16-разрядный параллельный. После записи данных в регистр RS формируется выходной сигнал «EN», формируются внутренние признаки EN и TR в регистре RC и схема формирования последовательного кода FK вырабатывает последовательный код на выходе DS, начиная со старшего разряда регистра RS, в сопровождении 16 импульсов синхронизации на выходе SYN.

Одновременно с выдачей регистр RS осуществляет преобразование последовательного кода, поступающего с входа DI, в параллельный код.

После окончания выдачи признак TR в регистре RC сбрасывается, после чего возможно корректное считывание полученного значения параллельного кода. Регистр доступен по записи и чтению, в исходном состоянии содержит нулевой код.

Тел.:(+7-499)720-89-92

Факс:(+7-495)913-21-92

## 3.5 Синхронизация МБИС при работе в троированной системе

Рассинхронизация работы параллельных интерфейсов между тремя каналами может составлять до одного такта частоты 12 МГц, поэтому работа трёх МБИС по параллельному интерфейсу ведётся асинхронно друг от друга.

При работе последовательного канала необходимо синхронизировать работу трёх МБИС. Из 12 МГц получается частота 4 МГц (выход СL), синхронная в трёх каналах. От 4 МГц работает последовательный канал. В зависимости от содержимого 12 и 13 разрядов регистра RC эта частота синхронно делится на 2, 4 или 8. Выходной сигнал межканальной синхронизации SS мажорируется и возвращается на вход SSM МБИС для синхронизации делителей частоты в трёх каналах.

По сигналу записи в регистр RS схема межканальной синхронизации вырабатывает сигнал начала обмена SN, который мажорируется и возвращается на вход SNM для синхронного запуска работы последовательного канала в троированной системе.

Тел.:(+7-499)720-89-92

Факс:(+7-495)913-21-92

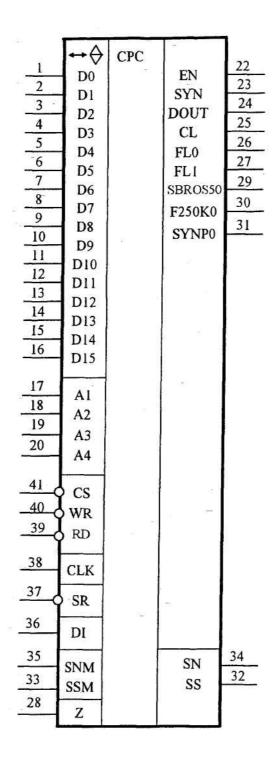

# 4 Условное графическое изображение МБИС

4.1 Условное графическое изображение МБИС представлено на рисунке 5

Рисунок 5 - Условное графическое изображение МБИС

Тел.:(+7-499)720-89-92

Факс:(+7-495)913-21-92