刀

ယ

တ

$\infty$

တ

$\infty$

(51) MITK **H03K** 3/00 (2006.01)

#### ФЕДЕРАЛЬНАЯ СЛУЖБА ПО ИНТЕЛЛЕКТУАЛЬНОЙ СОБСТВЕННОСТИ, ПАТЕНТАМ И ТОВАРНЫМ ЗНАКАМ

# (12) ОПИСАНИЕ ИЗОБРЕТЕНИЯ К ПАТЕНТУ

- (21), (22) Заявка: 2007142219/09, 15.11.2007

- (24) Дата начала отсчета срока действия патента: 15.11.2007

- (43) Дата публикации заявки: 27.05.2009

- (45) Опубликовано: 20.09.2009 Бюл. № 26

- (56) Список документов, цитированных в отчете о поиске: АСТАХАНОВСКИЙ А.Г. и др.

Апериодические автоматы. / Под ред. В.И. Варшавского. - М.: Наука, 1976, рис.2.9. SU 1277385 A1, 15.12.1986. SU 945960 A1, 23.07.1982. GB 1199698 A, 22.07.1970.

Адрес для переписки:

119333, Москва, ул. Вавилова, 44, к.2, Институт проблем информатики Российской академии наук (ИПИ РАН)

(72) Автор(ы):

Дьяченко Юрий Георгиевич (RU), Степченков Юрий Афанасьевич (RU), Морозов Николай Викторович (RU), Рождественский Юрий Владимирович (RU)

(73) Патентообладатель(и):

Институт проблем информатики Российской академии наук (ИПИ РАН) (RU)

(54) КОМБИНИРОВАННЫЙ Г-ТРИГГЕР С НУЛЕВЫМ СПЕЙСЕРОМ

(57) Реферат:

Изобретение относится к импульсной и вычислительной технике может использоваться при построении самосинхронных вычислительных устройств и систем цифровой обработки информации. Техническим результатом изобретения является возможность обеспечения индикации парафазных сигналов с нулевым спейсером наряду c инфазными. Этот результат достигается за счет введения в схему элемента ИЛИ-И-ИЛИ-НЕ и подключения парафазного и инфазного входов триггера к входам групп входов ИЛИ данного элемента. 2 н. и 6 з.п. ф-лы, 8 ил.

2 S

$\infty$ ဖ  $\infty$ 9 က 2

~

(51) Int. Cl. **H03K 3/00** (2006.01)

FEDERAL SERVICE FOR INTELLECTUAL PROPERTY, PATENTS AND TRADEMARKS

# (12) ABSTRACT OF INVENTION

(21), (22) Application: 2007142219/09, 15.11.2007

(24) Effective date for property rights: **15.11.2007**

(43) Application published: 27.05.2009

(45) Date of publication: 20.09.2009 Bull. 26

Mail address:

119333, Moskva, ul. Vavilova, 44, k.2, Institut problem informatiki Rossijskoj akademii nauk (IPI RAN)

(72) Inventor(s):

D'jachenko Jurij Georgievich (RU), Stepchenkov Jurij Afanas'evich (RU), Morozov Nikolaj Viktorovich (RU), Rozhdestvenskij Jurij Vladimirovich (RU)

(73) Proprietor(s):

Institut problem informatiki Rossijskoj akademii nauk (IPI RAN) (RU)

Z

N

ა 6

$\infty$

တ

$\infty$

2 368 068<sup>(13)</sup> C2

#### (54) COMBINED G-TRIGGER WITH ZERO SPACER

(57) Abstract:

FIELD: physics, computer engineering.

SUBSTANCE: invention is related to pulse and computer engineering and may be used in building of self-synchronous computer devices and systems of digital information processing. Technical result is achieved by introduction OR-AND-OR-NOT element in circuit and connection of paraphrase and inphase inputs of trigger to inputs of OR input groups of this element.

EFFECT: provision of possibility to provide

indication of paraphrase signals with zero spacer, as well as inphase signals.

C 7

2368068

Комбинированный гистерезисный триггер (Г-триггер) с нулевым спейсером относится к импульсной и вычислительной технике и может использоваться при построении самосинхронных вычислительных устройств и систем цифровой обработки информации.

Известен Г-триггер [1], содержащий элемент И-ИЛИ-НЕ и инвертор. Недостаток известного устройства - невозможность использовать его для индикации парафазных сигналов.

Более близким к предлагаемому решению по технической сущности и принятым в качестве прототипа является Г-триггер [2], содержащий три элемента И-ИЛИ-НЕ и инвертор.

Недостаток прототипа - невозможность использовать его для индикации инфазных сигналов и парафазных сигналов с нулевым спейсером.

Задача, решаемая в изобретении, заключается в обеспечении возможности индикации парафазных сигналов с нулевым спейсером наряду с инфазными.

Это достигается тем, что в Г-триггере, содержащем три входа, логический элемент с инверсией и выход, причем выход логического элемента с инверсией подключен к выходу триггера, введен элемент ИЛИ-И-ИЛИ-НЕ, первые два входа являются прямой и инверсной составляющими парафазного входа, третий вход является инфазным входом триггера, первый и второй входы первой и третьей групп входов ИЛИ элемента ИЛИ-И-ИЛИ-НЕ подключены к прямой и инверсной составляющим парафазного входа триггера, вход второй группы входов ИЛИ и третий вход третьей группы входов ИЛИ элемента ИЛИ-И-ИЛИ-НЕ соединены с инфазным входом, вход четвертой группы входов ИЛИ элемента ИЛИ-И-ИЛИ-НЕ подключен к выходу триггера, выход элемента ИЛИ-И-ИЛИ-НЕ соединен с входом логического элемента с инверсией, первая и вторая группы входов ИЛИ элемента ИЛИ-И-ИЛИ-НЕ, третья и четвертая группы входов ИЛИ элемента ИЛИ-И-ИЛИ-НЕ, третья и четвертая группы входов ИЛИ элемента ИЛИ-И-ИЛИ-НЕ, первая и вторая группы И элемента ИЛИ-И-ИЛИ-НЕ объединены во вторую группу И элемента ИЛИ-И-ИЛИ-НЕ.

Предлагаемое устройство удовлетворяет критерию "существенные отличия" Использование логического элемента с инверсией и элемента ИЛИ-И-ИЛИ-НЕ в составе схем Г-триггеров известно. Однако использование их в данном случае позволило достичь эффекта, выраженного целью изобретения.

Поскольку введенные конструктивные связи в аналогичных технических решениях не известны, устройство может считаться имеющим существенные отличия.

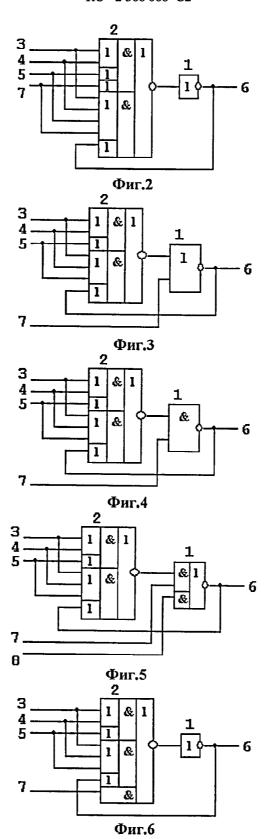

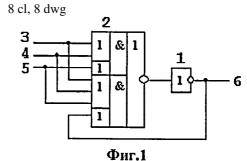

На фиг.1 изображена схема комбинированного Г-триггера с нулевым спейсером.

40

Схема комбинированного Г-триггера с нулевым спейсером содержит логический элемент с инверсией 1, реализованный на инверторе, элемент ИЛИ-И-ИЛИ-НЕ 2, прямую 3 и инверсную 4 составляющие парафазного входа, инфазный вход 5 триггера, первый и второй входы первой и третьей групп входов ИЛИ элемента ИЛИ-И-ИЛИ-НЕ 2 подключены к прямой 3 и инверсной 4 составляющим парафазного входа триггера, вход второй и третий вход третьей групп входов ИЛИ элемента ИЛИ-И-ИЛИ-НЕ 2 соединены с инфазным входом 5, вход четвертой группы входов ИЛИ элемента ИЛИ-И-ИЛИ-НЕ 2 подключен к выходу триггера 6 и выходу инвертора 1, выход элемента ИЛИ-И-ИЛИ-НЕ 2 соединен с входом инвертора 1, первая и вторая группы входов ИЛИ элемента ИЛИ-И-ИЛИ-НЕ 2, третья и четвертая группы входов ИЛИ элемента ИЛИ-И-ИЛИ-НЕ 2 объединены во вторую группу И элемента

ИЛИ-И-ИЛИ-НЕ 2, первая и вторая группы И элемента ИЛИ-И-ИЛИ-НЕ 2 объединены в выходную группу ИЛИ этого элемента.

Особенности данной схемы по сравнению с прототипом следующие.

В качестве входов Г-триггера используются как инфазный вход, так и парафазный вход с нулевым спейсером. В практических самосинхронных схемах это позволяет в ряде случаев упростить аппаратную реализацию схемы и повысить ее быстродействие за счет отказа от использования дополнительных логических элементов, формирующих инфазный индикаторный сигнал на основе парафазного со спейсером.

Таким образом, предлагаемое устройство обеспечивает возможность индикации парафазных сигналов с нулевым спейсером наряду с инфазными. Цель изобретения достигнута.

Схема Г-триггера работает следующим образом.

Пусть Г-триггер находится в спейсере. Это означает, что на его инфазнй 5 и парафазный 3-4 входы подается состояние логического "0" (низкий уровень сигнала), на входе инвертора 1 высокий уровень, на его выходе 6 - низкий уровень. Для переключения Г-триггера в противоположное состояние (высокий уровень на выходе 6) необходимо и достаточно подать на парафазный вход 3-4 рабочее состояние ("01" или "10"), а на инфазный вход 5 высокий уровень (логическую "1"). В этом случае выход элемента ИЛИ-ИЛИ-НЕ 2 переходит в состояние "0", а выход инвертора 1 переключится в состояние логической "1" (рабочее состояние) и через вход четвертой группы входов ИЛИ элемента ИЛИ-ИЛИ-НЕ замкнет обратную связь на вход инвертора 1, позволяя сохранять рабочее состояние Г-триггера до тех пор, пока на инфазный и парафазный входы триггера не поступит спейсер.

Таким образом, комбинированный Г-триггер с нулевым спейсером выполняет логическую функцию

$G=(P+PB)\cdot I+G\cdot (I+P+PB),$

5

10

30

где I - инфазный вход  $\Gamma$ -триггера; P, PB - прямая и инверсная составляющая парафазного входа, G - выход  $\Gamma$ -триггера.

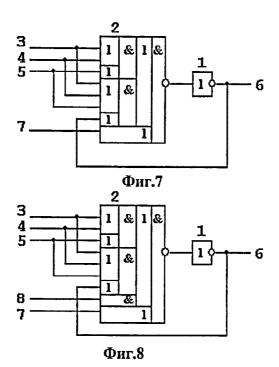

На фиг.2 представлена схема комбинированного Г-триггера с нулевым спейсером, с двумя инфазными и одним парафазным входами. Она отличается от схемы на фиг.1 наличием пятой группы входов ИЛИ элемента ИЛИ-И-ИЛИ-НЕ 2 и еще одним инфазным входом 7, подключенным к входу пятой группы входов ИЛИ и четвертому входу третьей группы входов ИЛИ элемента ИЛИ-И-ИЛИ-НЕ 2, пятая группа входов ИЛИ объединена в первую группу И вместе с первой и второй группами входов ИЛИ элемента ИЛИ-И-ИЛИ-НЕ 2.

Схема комбинированного Г-триггера с нулевым спейсером, с двумя инфазными и одним парафазным входами работает аналогично схеме комбинированного Г-триггера с нулевым спейсером, с одним инфазным и одним парафазным входами Ее функционирование описывается следующей логической формулой:

$$G=(P+PB)\cdot I_1\cdot I_2+G\cdot (I_1+I_2+P+PB),$$

где  $I_1, I_2$  - инфазные входы  $\Gamma$ -триггера; P, PB - прямая и инверсная составляющая парафазного входа; G - выход  $\Gamma$ -триггера.

На фиг.3 представлена схема комбинированного Г-триггера с нулевым спейсером, с одним инфазным и одним парафазным входами и входом установки нуля. Она отличается от схемы на фиг.1 тем, что введен вход установки нуля 7, а логический элемент с инверсией 1 реализован на элементе ИЛИ-НЕ, первый вход которого подключен к выходу элемента ИЛИ-И-ИЛИ-НЕ 2, а второй вход соединен с входом установки нуля 7.

Установка нуля осуществляется подачей высокого уровня сигнала на вход установки 7.

На фиг.4 представлена схема комбинированного Г-триггера с нулевым спейсером, с одним инфазным и одним парафазным входами и входом установки единицы. Она отличается от схемы на фиг.1 тем, что введен вход установки единицы 7, а логический элемент с инверсией 1 реализован на элементе И-НЕ, первый вход которого подключен к выходу элемента ИЛИ-И-ИЛИ-НЕ 2, а второй вход соединен с входом установки единицы 7.

Установка единицы осуществляется подачей низкого уровня сигнала на вход установки 7.

10

На фиг.5 представлена схема комбинированного Г-триггера с нулевым спейсером, с одним инфазным и одним парафазным входами и входами установки нуля и единицы Она отличается от схемы на фиг.1 тем, что введены входы установки единицы 7 и нуля 8, а логический элемент с инверсией 1 реализован на элементе И-ИЛИ-НЕ, первый вход первой группы входов И элемента И-ИЛИ-НЕ 1 подключен к выходу элемента ИЛИ-ИЛИ-НЕ 2, второй вход первой группы входов И элемента И-ИЛИ-НЕ 1 соединен с входом установки единицы 7, вход второй группы входов И элемента И-ИЛИ-НЕ 1 подключен к входу установки нуля 8.

Установка нуля осуществляется подачей высокого уровня сигнала на вход установки нуля 8. Установка единицы осуществляется подачей низкого уровня сигнала на входы установки 7 и 8.

Представленные на фиг.3-5 схемы с входами установки приводят к ухудшению нагрузочной способности выхода триггера и характеризуются тем, что установка нуля осуществляется подачей высокого уровня сигнала на вход установки нуля, а установка единицы - подачей низкого уровня сигнала на входы установки. Однако установку нуля и единицы можно осуществить и другими способами.

На фиг.6 представлена схема комбинированного Г-триггера с нулевым спейсером, с одним инфазным и одним парафазным входами и входом установки единицы. Она отличается от схемы на фиг.1 тем, что введен вход установки единицы 7 и в элемент ИЛИ-И-ИЛИ-НЕ 2 введена третья группа И, введен вход установки единицы 7 подключен к входу третьей группы входов И элемента ИЛИ-И-ИЛИ-НЕ 2, все группы И элемента ИЛИ-И-ИЛИ-НЕ 2 объединены в выходную группу ИЛИ этого элемента.

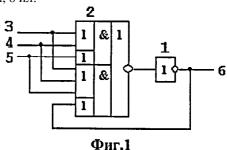

Установка единицы осуществляется подачей высокого уровня сигнала на вход установки 7. На фиг.7 представлена схема комбинированного Г-триггера с нулевым спейсером, с одним инфазным и одним парафазным входами и входом установки нуля. Она отличается от схемы на фиг.1 тем, что введен вход установки нуля 7 и элемент ИЛИ-И-ИЛИ-НЕ заменен на элемент ИЛИ-И-ИЛИ-И-НЕ 2, выход которого подключен к входу логического элемента с инверсией 1, чей выход соединен с выходом 6 триггера, первые два входа 3 и 4 являются прямой и инверсной составляющими парафазного входа, третий вход 5 является инфазным входом триггера, первый и второй входы первой и третьей групп входов ИЛИ элемента ИЛИ-И-ИЛИ-И-НЕ подключены к прямой 3 и инверсной 4 составляющим парафазного входа триггера, вход второй группы входов ИЛИ и третий вход третьей группы входов ИЛИ элемента ИЛИ-И-ИЛИ-И-НЕ соединены с инфазным входом 5, вход четвертой группы входов ИЛИ элемента ИЛИ-И-ИЛИ-И-НЕ подключен к выходу 6 триггера, выход элемента ИЛИ-И-ИЛИ-И-НЕ 2 соединен с входом логического элемента с инверсией 1, первая и вторая группы входов ИЛИ элемента

ИЛИ-И-ИЛИ-И-НЕ 2 объединены в первую группу И элемента ИЛИ-И-ИЛИ-И-НЕ 2, третья и четвертая группы входов ИЛИ элемента ИЛИ-И-ИЛИ-И-НЕ 2 объединены во вторую группу И элемента ИЛИ-И-ИЛИ-И-НЕ 2, первая и вторая группы И элемента ИЛИ-И-ИЛИ-И-НЕ 2 объединены в первую выходную группу ИЛИ элемента ИЛИ-И-ИЛИ-И-НЕ 2, вход установки нуля подключен к входу пятой группы входов ИЛИ элемента ИЛИ-И-ИЛИ-И-НЕ 2, которая одновременно является второй выходной группой ИЛИ элемента ИЛИ-И-ИЛИ-И-НЕ 2, первая и вторая выходная группы ИЛИ элемента ИЛИ-И-ИЛИ-И-НЕ 2 объединены в выходную группу И этого элемента.

Установка нуля осуществляется подачей низкого уровня сигнала на вход установки 7. На фиг.8 представлена схема комбинированного Г-триггера с нулевым спейсером, с одним инфазным и одним парафазным входами и входами установки нуля и единицы. Она отличается от схемы на фиг.7 тем, что в схему введен вход установки единицы 8, а в элемент ИЛИ-И-ИЛИ-И-НЕ 2 введена третья группа И, вход установки единицы 8 подключен к входу третьей группы И элемента ИЛИ-И-ИЛИ-И-НЕ 2, которая объединена в первую выходную группу ИЛИ элемента ИЛИ-И-ИЛИ-И-НЕ 2 вместе с двумя остальными группами И.

Установка нуля осуществляется подачей низкого уровня сигнала на вход установки 8. Установка единицы осуществляется подачей высокого уровня сигнала на входы установки 7 и 8.

Источники информации

30

- [1] Астахановский А.Г., Варшавский В.И., Мараховский В.Б. и др. Апериодические автоматы. // Под ред. В.И.Варшавского. М.: Наука, 1976. рис.2.8 (б).

- [2] Астахановский А.Г., Варшавский В.И., Мараховский В.Б. и др. Апериодические автоматы. // Под ред. В.И.Варшавского. М.: Наука, 1976. рис.2.9.

### Формула изобретения

- 1. Комбинированный Г-триггер с нулевым спейсером, содержащий три входа, логический элемент с инверсией и выход, причем выход логического элемента с инверсией подключен к выходу триггера, отличающийся тем, что в схему введен элемент ИЛИ-И-ИЛИ-НЕ, первые два входа являются прямой и инверсной составляющими парафазного входа, третий вход является инфазным входом триггера, первый и второй входы первой и третьей групп входов ИЛИ элемента ИЛИ-И-ИЛИ-НЕ подключены к прямой и инверсной составляющим парафазного входа триггера, вход второй группы входов ИЛИ и третий вход третьей группы входов ИЛИ элемента ИЛИ-И-ИЛИ-НЕ соединены с инфазным входом, вход четвертой группы входов ИЛИ элемента ИЛИ-И-ИЛИ-НЕ подключен к выходу триггера, выход элемента ИЛИ-И-ИЛИ-НЕ соединен с входом логического элемента с инверсией, первая и вторая группы входов ИЛИ элемента ИЛИ-И-ИЛИ-НЕ объединены в первую группу И элемента ИЛИ-И-ИЛИ-НЕ, третья и четвертая группы входов ИЛИ элемента ИЛИ-И-ИЛИ-НЕ объединены во вторую группу И элемента ИЛИ-И-ИЛИ-НЕ, первая и вторая группы И элемента ИЛИ-И-ИЛИ-НЕ объединены в выходную группу ИЛИ элемента ИЛИ-И-ИЛИ-НЕ.

- 2. Комбинированный Г-триггер с нулевым спейсером по п.1, отличающийся тем, что в схему введены второй инфазный вход, четвертый вход в третью группу входов ИЛИ элемента ИЛИ-И-ИЛИ-НЕ и пятая группа входов ИЛИ в элемент ИЛИ-И-ИЛИ-НЕ, второй инфазный вход подключен к входу пятой группы входов ИЛИ и четвертому входу третьей группы входов ИЛИ элемента ИЛИ-И-ИЛИ-НЕ,

пятая группа входов ИЛИ объединена в первую группу И вместе с первой и второй группами входов ИЛИ элемента ИЛИ-И-ИЛИ-НЕ.

- 3. Комбинированный Г-триггер с нулевым спейсером по п.1, отличающийся тем, что в схему введен вход установки нуля, логический элемент с инверсией реализован на элементе ИЛИ-НЕ, первый вход которого подключен к выходу элемента ИЛИ-И-ИЛИ-НЕ, а второй вход соединен с входом установки нуля.

- 4. Комбинированный Г-триггер с нулевым спейсером по п.1, отличающийся тем, что в схему введен вход установки единицы, логический элемент с инверсией реализован на элементе И-НЕ, первый вход которого подключен к выходу элемента ИЛИ-И-ИЛИ-НЕ, а второй вход соединен с входом установки единицы.

- 5. Комбинированный Г-триггер с нулевым спейсером по п.1, отличающийся тем, что в схему введены входы установки нуля и единицы, а логический элемент с инверсией реализован на элементе И-ИЛИ-НЕ, первый вход первой группы входов И элемента И-ИЛИ-НЕ подключен к выходу элемента ИЛИ-И-ИЛИ-НЕ, второй вход первой группы входов И элемента И-ИЛИ-НЕ соединен с входом установки единицы, вход второй группы входов И элемента И-ИЛИ-НЕ подключен к входу установки нуля.

- 6. Комбинированный Г-триггер с нулевым спейсером по п.1, отличающийся тем, что в схему введен вход установки единицы, в элемент ИЛИ-И-ИЛИ-НЕ введена третья группа И, вход установки единицы подключен к входу третьей группы И элемента ИЛИ-И-ИЛИ-НЕ, все группы И элемента ИЛИ-И-ИЛИ-НЕ объединены в выходную группу ИЛИ этого элемента.

25

- 7. Комбинированный Г-триггер с нулевым спесером, содержащий три входа, логический элемент с инверсией и выход, причем выход логического элемента с инверсией подключен к выходу триггера, отличающийся тем, что в схему введены вход установки нуля и элемент ИЛИ-И-ИЛИ-И-НЕ, первые два входа являются прямой и инверсной составляющими парафазного входа, третий вход является инфазным входом триггера, первый и второй входы первой и третьей групп входов ИЛИ элемента ИЛИ-И-ИЛИ-И-НЕ подключены к прямой и инверсной составляющим парафазного входа триггера, вход второй группы входов ИЛИ и третий вход третьей группы входов ИЛИ элемента ИЛИ-И-ИЛИ-И-НЕ соединены с инфазным входом, вход четвертой группы входов ИЛИ элемента ИЛИ-И-ИЛИ-И-НЕ подключен к выходу триггера, выход элемента ИЛИ-И-ИЛИ-И-НЕ соединен с входом логического элемента с инверсией, первая и вторая группы входов ИЛИ элемента ИЛИ-И-ИЛИ-И-НЕ объединены в первую группу И элемента ИЛИ-И-ИЛИ-И-НЕ, третья и четвертая группы входов ИЛИ элемента ИЛИ-И-ИЛИ-И-НЕ объединены во вторую группу И элемента ИЛИ-И-ИЛИ-И-НЕ, первая и вторая группы И элемента ИЛИ-И-ИЛИ-И-НЕ объединены в первую выходную группу ИЛИ элемента ИЛИ-И-ИЛИ-И-НЕ, вход установки нуля подключен к входу пятой группы входов ИЛИ элемента ИЛИ-И-ИЛИ-И-НЕ, которая одновременно является второй выходной группой ИЛИ элемента ИЛИ-И-ИЛИ-И-НЕ, первая и вторая выходная группы ИЛИ элемента ИЛИ-И-ИЛИ-И-НЕ объединены в выходную группу И этого элемента.

- 8. Комбинированный Г-триггер с нулевым спейсером по п.7, отличающийся тем, что в схему введен вход установки единицы, а в элемент ИЛИ-И-ИЛИ-И-НЕ введена третья группа И, вход установки единицы подключен к входу третьей группы И элемента ИЛИ-И-ИЛИ-И-НЕ, которая объединена в первую выходную группу ИЛИ элемента ИЛИ-И-ИЛИ-И-НЕ вместе с двумя остальными группами И.